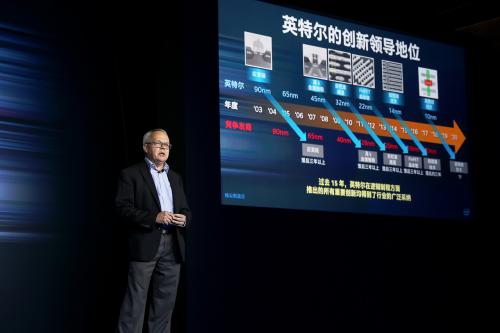

英特尔在工艺制程领域的造诣可谓登峰造极。2003年,英特尔推出应变硅90nm芯片,当时属于首家,领先业界三年;2007年,英特尔生产出高K金属栅极的芯片,三年后业内其它公司才推出类似产品;英特尔的32nm工艺具有“自校准通道”的技术专长,能够加强连接点的能力,互联功能对于缩小晶片面积提升密度极其重要的,同样领先业界三年。再到22nm技术,英特尔在2011年成为第一家推出了FinFET工艺的厂商,三年后市场上才出现类似产品。英特尔高级院士、技术与制造事业部制程架构与集成总监Mark Bohr总结,“在过去15年中,英特尔在逻辑制程方面推出所有创新都得到了行业的广泛采纳。”

摩尔定律已经失效?还会持续十年

这几年,英特尔的工艺制程迟迟不做更新,这让业界一度怀疑摩尔定律已死。近日,在 “领先?无界”英特尔精尖制造日上,Mark Bohr给出肯定的回答:摩尔定律继续有效。可能有人进一步追问:摩尔定律还会持续多久?Mark Bohr回答地意味深远:“如果你在20年前问半导体业内专家,他们会告诉你摩尔定律还能继续十年,如果你在10年前再问行业专家,他们还会说十年,现在你问我,我还是会回答十年。我们拿海平面打一个比方,你离海平线越来越近,但它还是不断往前推进的。”

英特尔高级院士、技术与制造事业部制程架构与集成总监Mark Bohr

英特尔原来的产品策略是Tick-Tock,一年更新一代产品,另一年更新一代工艺,从14nm周期开始拉长,14nm的更新经过了两年半还多,10nm花费了三年多。用户更关心的是英特尔后续是否回归到Tick-Tock策略上?英特尔公司全球副总裁逻辑技术开发部练习总监白鹏表示,“关于产品策略,我们每年有一个新产品,也可以说是同一技术,比如10纳米产品我们有三个wave(三代产品)出来。从产品策略上不会回到Tick-Tock。从技术节奏角度来讲,14nm和10nm,我们迈的步子比较大一点,所以时间也长一点,还要看具体的技术,我迈多大的步子,这和时间会有关系,我们还是会维持在两到三年的节奏。”

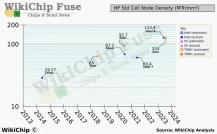

启用“失宠”的计算公式,揭开真正10nm的面纱

晶体管密度一直是工艺制程命名的主要标准,摩尔定律是指每代制程工艺都要让芯片上的晶体管数量翻一番。纵观芯片每代创新历史,业界一直遵循这一定律,并按前一代制程工艺缩小约0.7倍来对新制程节点命名,这种线性微缩意味着晶体管密度翻番。因此,出现了90nm、65nm、45nm、32nm——每一代制程节点都能在给定面积上,容纳比前一代多一倍的晶体管。再后来,制程进一步微缩越来越难,一些公司背离了摩尔定律的法则。即使晶体管密度增加很少,或者根本没有增加,但他们仍继续为制程工艺节点命新名。结果导致这些新的制节点名称偏离了摩尔定律曲线的正确位置。

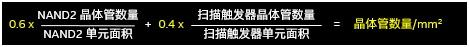

一般我们理解的摩尔定律计算公式是用栅极距乘以最小金属距,但是这并不包含逻辑单元设计,而逻辑单元设计才会影响真正的晶体管密度。因此英特尔重新启用曾经流行但一度“失宠”的一个计算公式了,它基于标准逻辑单元的晶体管密度,并包含决定典型设计的多个权重因素。

Mark Bohr解释,“如果采用这种方式计算,从45纳米到32纳米一路到14纳米、10纳米,英特尔密度的提升是非常明显的,14纳米和10纳米我们做到的密度提升要比之前做的更多一些。这些14纳米和10纳米之所以做到密度更多的提升是因为用了超微缩技术,使得我们在密度上得到更大优化,分别为2.5倍和2.7倍。通过超微缩技术,10纳米将能够做到7.6平方毫米,这是一个0.43的系数。所以也意味着能耗功耗更低,密度和性能得到了提升。”

关于这一公式,笔者最大的疑惑就是出处在哪里?是否具有权威性?Mark Bohr的回答是,“这不是英特尔新创立的公式,而是存在很多年的,而且我们的客户也呼吁我们站出来对摩尔定律做出解释。”

10nm、22FFL制程亮相,英特尔领先业界三年

本次发布会的亮点要属10nm和22FFL制程的闪亮登场。

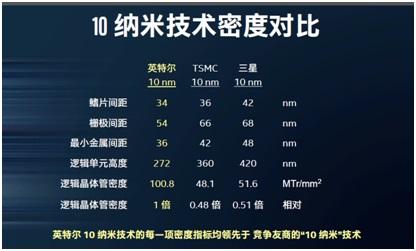

英特尔10纳米制程的最小栅极间距从70纳米缩小至54纳米,且最小金属间距从52纳米缩小至36纳米。尺寸的缩小使得逻辑晶体管密度可达到每平方毫米1.008亿个晶体管,是之前英特尔14纳米制程的2.7倍,大约是业界其他“10纳米”制程的2倍。

相比之前的14纳米制程,英特尔10纳米制程提升高达25%的性能和降低45%的功耗。相比业界其他所谓的“10 纳米”,英特尔10纳米制程也有显着的领先性能。全新增强版的10 纳米制程——10+ +,则可将性能再提升15%或将功耗再降低30%。

和友商制程进行对比

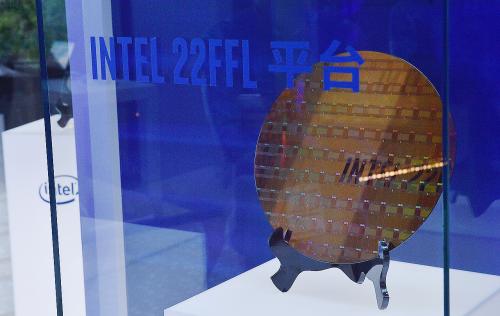

基于多年22纳米/14纳米的制造经验,英特尔推出了称为22FFL(FinFET低功耗)的全新工艺。该工艺提供结合高性能和超低功耗的晶体管,及简化的互连与设计规则,能够为低功耗及移动产品提供通用的FinFET设计平台。与先前的22GP(通用)技术相比,全新22FFL技术的漏电量最多可减少100倍。22FFL工艺还可达到与英特尔14纳米晶体管相同的驱动电流,同时实现比业界28纳米/22纳米平面技术更高的面积微缩。

联手ARM进行晶圆代工:“老虎”要发威了

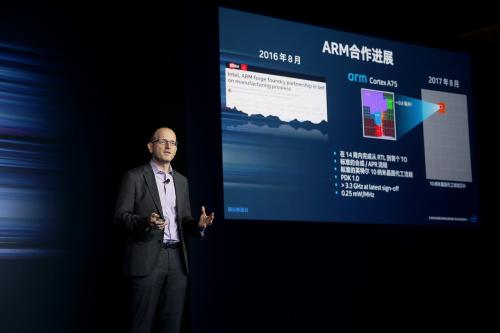

英特尔要做晶圆代工,这个消息已经让业界很震惊,而且合作伙伴还是ARM,其中最新发布的10nm CPU测试芯片流片还具有先进的ARM CPU内核,英特尔把ARMCortex A75放到英特尔标准的晶圆代工的流程当中,使用标准的行业设计实现,电子设计自动化Place and Route工具和流程,性能高达3GHz以上。其中IP由ARM提供,只花了14周时间就完成了RTL到首个流片。同时,ARM在开发高性能的存储器、逻辑单元和CPU POP套件,以进一步扩展下一代ARM CPU在英特尔 10nm技术上的性能水平。

按照商业逻辑,ARM和英特尔应该是竞争对手关系,他们的联手有着怎样的意义?英特尔公司技术与制造事业部副总裁、晶圆代工业务联席总经理 Zane Ball解释,“第一,所有客户都希望产品上市时间缩短,这就要求代工非常标准化,非常高效,我们设计自动化的平台要非常有效地和整个生态系统能够配合起来。我们需要一个强有力的知识产权生态链,这样使得我们在整个的晶圆制造行业里面,让企业可以相互配合;第二,所有客户都要低能耗,不管是14nm、22nm,还是10nm,所有企业都希望看到单元面积减小,尺寸减小,功耗降低。因此,功耗和性能比极其重要,这也意味着很多市场非常重视的IP。英特尔和ARM之间形成合作伙伴关系,把ARMCortex A75放到英特尔标准的晶圆代工的流程当中,所以整个流程是标准化的。”

英特尔公司技术与制造事业部副总裁晶圆代工业务联席总经理Zane A.Ball

英特尔为什么要做晶圆代工?英特尔公司全球副总裁兼中国区总裁杨旭只回答了一句话:“老虎不说话,以为是病猫。”说这句话的底气是英特尔的精尖制造实力,笔者不想多讲,只想分析一下晶圆代工和自身产品的发展平衡。有两点个问题:一是有在竞争关系的公司都让同一晶圆厂来做是否合理?Zane Ball表示,“我们愿意合作,要让这样的合作能够做成。第一,我们要明确的保护知识产权,我们有非常广泛的信息系统,代工厂的业务集团和其他的业务集团是不一样的。第二,客户在供应方面会获得优先,同时在流程方面也会有平等的、透明的安排。所以这是一个非常明确的公司内部政策来处理代工业务,不会有障碍。”二是开放尖端代工业务对自身CPU有没有影响,是否需要适当放缓代工?Zane Ball指出,“我们的策略是非常简单的,我们不断的在技术上推陈出新,和我们客户保持同步的增长,满足他们的需求,尽可能快的发展我们的业务。所以,我们不会有任何顾虑是不是要适当减缓我们发展的步骤,我们开足马力,全力以赴用我们的技术和创新为客户服务、为市场服务,尽可能快的发展。”