前言:

5nm、3nm节点主要面向FPGA等高性能计算领域,智能处理器和5G芯片。在接下来的两三年中,5G将会被大规模使用。

台积电:最为积极和最早布局

很快台积电的5nm工艺即将量产,与此同时,台积电的3nm工艺也在持续推进当中。

去年7月,台积电就公开表示其 3nm 工艺的开发进展顺利,并且已经与早期客户就技术定义进行了接触。

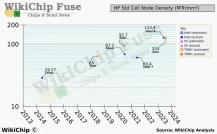

近日,台积电正式披露了其最新3nm工艺的细节详情,其晶体管密度达到了惊人的2.5亿个/mm2。

在性能提升方面,台积电5nm工艺相比7nm性能可提升15%,能效比提升30%,而3nm较5nm性能则可进一步提升7%,能效比提升15%。

台积电在评估多种选择后认为现行的FinFET工艺在成本及能效上更佳,所以3nm首发依然会是FinFET晶体管技术。

而台积电则表示,其3nm工艺研发符合预期,并没有受到疫情影响,预计在2021年进入风险试产阶段,2022年下半年量产。

3nm是他们在5nm之后在芯片工艺上的一个完整的技术跨越,同第一代的5nm工艺(N5)相比,第一代的3nm工艺(N3)的晶体管密度将提升约70%,速度提升10%到15%,芯片的性能提升25%到30%,3nm工艺将进一步夯实他们未来在芯片工艺方面的领导地位。

台积电通过了1,217.81亿元资本预算,除升级先进制程产能外,也用于转换部分逻辑制程产能为特殊制程产能。

台积电预定今年度资本支出金额约100亿美元至110亿美元,其中80%经费将用于3 纳米、5纳米及7纳米先进制程技术。

台积电预期,今年7纳米与第二代7纳米制程将贡献约25%业绩。另外有10%经费用于先进封装与光罩,10%用于特殊制程。

面对三星积极冲刺晶圆代工,并企图在3 纳米制程超车台积电,台积电发言系统表示,不对竞争对手的技术发展做任何评论,并强调绝有信心在7纳米、5纳米,甚至3纳米制程持续维持全球领先地位。