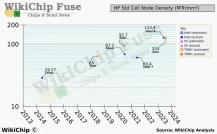

7nm之后英特尔还会进入5nm节点,时间点会在2023年,按照英特尔的水平,至少也是2x缩放,那晶体管密度至少会达到4亿/mm2,远远超过台积电的3nm工艺水平,台积电的2nm工艺在2023年之前应该没戏的。

目前的计算还是理论性的,但是只要英特尔的工艺路线重回正轨,先进工艺上追回来并不让人意外,台积电、三星并不能小觑半导体一哥的技术实力。

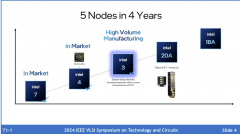

7nm之后是更先进的5nm、3nm、2nm和1.4nm,其中5nm、3nm和2nm处在路线发现阶段,分别计划在2023年、2025年和2027年采用,2029年拟开始采用1.4nm工艺。

同时,英特尔或也将在5nm工艺阶段放弃FinFET晶体管,转向GAA环绕栅极晶体管。

其首席财务官也曾指出,英特尔要进行10nm量产、7nm提速、5nm投资,考虑到这部分技术交集主要集中在2020~2021年,也必然会影响到英特尔毛利率。

从流程路线图来看,英特尔将按照每两年一次主要节点更新的节奏进行。而3nm,排到了2025年来实现。

决战3nm面临的挑战

①虽说现在台积电和三星的7nm EUV产品已经步入正轨,但当先进工艺推进到3nm之时,与之相关的EUV技术也将再次发生变化。

而这就涉及了EUV曝光技术的开发方面最重要的是EUV曝光设备的改良。

②EUV掩膜、检测掩膜的缺陷以及光源功率等都将影响EUV技术在先进工艺上的使用。

③虽然台积电、三星以及英特尔都计划在GAA上有所投入,但在3nm初期阶段就采用新型晶体管,是否能够被市场接纳,也是值得厂商思考的事情。

④如果采用GAA工艺,则需要导入新材料,因此制程技术上相当困难,尤其是在蚀刻部分是大挑战。

⑤3nm工艺节点的互连是芯片中的微小铜布线方案,它在每个节点上变得越发紧凑,造成芯片中不必要的RC延迟。

结尾:

纵观全球半导体制程玩家,目前仅剩三足鼎立:英特尔、三星和台积电。而其中真正卯着劲在攻坚3nm的,其实只有三星和台积电两家而已。从市场份额来看,台积电暂时领先。