高级制程的加速演化、复杂性和成本的飙升以及对IP可用性的担忧正在引发一些难题。

随着摩尔定律物理极限的日益临近,人们普遍预测称,由于成本上升以及在先进工艺上开发芯片的难度增加,芯片尺寸缩放将逐步放缓,但是现实正好相反,前沿工艺节点的推出速度反而正在加快。

成本确实在上升,同时,由于多重图案化、芯片上集成更多器件、和三维晶体管密度相关的物理效应、更多功能和细化电介质造成复杂性飙升,设计规则数量也在急剧增长。除此之外,最先进的节点上是否有可用IP,以及使用代工厂最新版本制造工艺时能否进行充分测试和特征分析的不确定性也在增加。

“过去,当你从一种工艺切换到另一种工艺上时,人们会认为,你已经完成了你的设计,所以不会有什么大不了的问题,”eSilicon IP工程副总裁Deepak Sabharwal说。 “你所做的工作就是将原理图进行缩放,并根据新规则重新布局布线。工艺节点只是一个数字,无论是40nm还是90nm都没关系,本质上没有什么区别。而且,从人们的期望来讲,也希望完成了上一个节点的设计之后,能够大量重复使用既有的资源和成果,快速前进到下一个节点上。”

这种演进模式在两维结构下非常有效,但是随着finFET的推出,情况出现了显著的变化。

Sabharwal说:“在finFET中,器件垂直放置,所以现在硅片面积的约束条件是金属层。晶圆代工厂一直在努力,如何比之前的节点以更紧密的间距进入金属层。 现在的设计规则非常严苛,设计规则手册厚达数千页,布局团队挖空心思琢磨如何在不影响其它层的情况下进行更改。这就像一个多米诺骨牌效应,你在设计中做一个很小的改变,就会影响其他10个地方。今天,设计如此紧密,组合如此精细,每个地方都有严格的容差和阈值范围,设计和制造都变得非常困难了。”

这也意味着设计工程师和布局工程师需要每天都在一起工作,因为如果布局团队在某个地方进行了重大调整,就可能会在其他地方产生问题,需要设计工程师重新修改设计。尽管如此,虽然这些问题还是会经常出现,一些公司仍然在加速升级制造工艺。

Cadence公司知识产权部业务发展总监Tom Wong表示:“业界从90nm过渡到65nm花了将近四年的时间。从65纳米到55纳米,然后再到40纳米花了将近三年的时间。 从40纳米平面工艺过渡到28纳米高k/金属门(HKMG)也用了大约三年的时间。之后的工艺升级就出现了加速趋势。从28nm HKMG到20nm只用了两年左右的时间,从20nm HKMG到16nm finFET用了不到两年的时间,16纳米到14纳米不到一年,然后不到一年,就到了10纳米。尽管刚刚在不到一年前开始生产10纳米晶圆,我们现在已经前进到了7纳米世代。”

Tom Wong表示,随着工艺尺寸日益精细,投资新晶圆厂需要高额研发成本和巨大的资本支出,人们普遍预计参与最前沿工艺升级的代工厂越来越少。“但是实际情况却完全不同,在16nm节点时,至少有四家大型晶圆代工厂参与角逐,到了7nm时,还至少有三家公司争夺领先地位。”

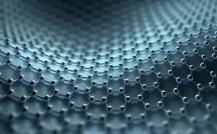

图 与日俱增的复杂度和设计规则

经济性考虑

工艺升级的经济性对设计上游影响巨大。芯片行业依赖于IP复用,更精确地说,是IP可以从一个节点到另一个节点之间迁移,以维持经济可行性。但是现在,IP复用越来越难。

“当你的工艺节点过渡到下一个更精细的几何尺寸时,当标称Vdd从0.8V下降到0.7V时会发生什么? 这将使得您预期比较简单的IP迁移项目变成针对复杂IP(如高速SerDes)的全面重新设计,“Wong说。 “另外,您可以利用的设计余量更少了,时序收敛也更复杂,还需要更多得考虑如何在模拟中管理OCV(片上变化)。 这往往会增加IP支持的成本,并延长部署时间。”

更加雪上加霜的是,在新工艺诞生的过程中,还需要并行进行大量的SoC开发,开发设计支持工具和IP。这意味着,当新工艺最终成熟或做好可以大规模生产的准备时,可能需要重新更新IP。这样一来,不仅IP开发过程更加困难和昂贵,芯片开发过程也会变得成本高昂。

eSilicon的Sabharwal表示:“从16/14nm到7nm的过渡过程中,我发现我们投入的资源是上次工艺升级的1.5倍。”

硬IP与软IP,大节点与小节点

在这个规则约束不断更新的世界中,硬IP的迁移变得特别困难。

“当我们谈论硬IP的迁移难度时,首先,它在很大程度上取决于这次是否只是迁移到新的半节点,即所谓的小节点上,因为小节点只是对节点的增量升级,”Arteris IP的解决方案架构师Benny Winefeld说。 “全新节点的迁移总是很难,但过渡到半节点的可行性更高,因为它主要只涉及到光学特性的缩小。DRC规则相似,各种电气特性的变化也基本一样,要么多一些,要么少一些,总之是可预测的。”

他指出,台积电的32纳米到28纳米的迁移就是一个很好的例子。 “我不会说这很容易,但它是完全可行的。在最近的节点中,DRC规则集的规模变得更大更复杂,规则从数百条增加到数千条。另外,大节点和半节点之间的差异也增加了,所以它们的相似度越来越低。从我最近的经验来看,台积电的16nm和12nm本来应该只是一个渐进式的升级,但是它们之间存在相当大的差异。如果您正在尝试使用调整多边形的智能工具来自动转换,现在需要执行更复杂的转换。不是只乘上一个0.8的线性比例就万事大吉了。因为这种变化不仅会突然违反物理规则,也可能造成电气特性的显着变化甚至失效。在台积电的12nm中,DRC规则不同,所用库也不同。但即便如此,人们也一般认为台积电的12纳米是一个渐进式的变化。”