日前,有消息称,比利时研究机构Imec和微影设备制造商ASML计划成立一座联合研究实验室,共同探索在后3nm逻辑节点的奈米级元件制造蓝图。此次双方这项合作是一项为期五年计划的一部份,分为两个阶段:

首先是开发并加速极紫外光(EUV)微影技术导入量产,包括最新的EUV设备准备就绪。

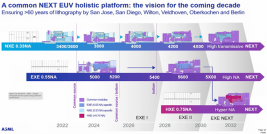

其次将共同探索下一代高数值孔径(NA)的EUV微影技术潜力,以便能够制造出更小型的奈米级元件,从而推动3nm以后的半导体微缩。

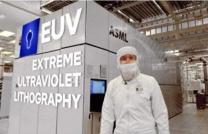

极紫外光(EUV)微影技术

EUV光刻也叫极紫外光刻,它以波长为10-14 nm的极紫外光作为光源的光刻技术。具体为采用波长为13.4nm 的软x射线。极紫外线就是指需要通过通电激发紫外线管的K极然后放射出紫外线。

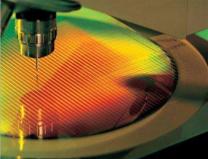

光刻技术是现代集成电路设计上一个最大的瓶颈。现cpu使用的45nm、32nm工艺都是由极紫外光液浸式光刻系统来实现的,但是因受到波长的影响还在这个技术上有所突破是十分困难的,但是如采用EUV光刻技术就会很好的解决此问题,很可能会使该领域带来一次飞跃。涉及到生产成本问题,由于极紫外光刻是目前能力最强且最成熟的技术,能够满足精确度和成本要求,所以其工艺的延伸性非常强,很难被取代。因而在光刻技术方面,在22/20nm的节点上,主要几家芯片厂商也将继续使用极紫外光液浸式光刻系统的双重成像技术。

价格昂贵且延迟已久的EUV系统将成为主流工具?

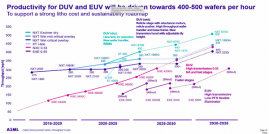

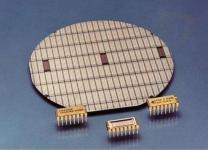

台积电、英特尔都把研发主力寄望于,这台史上最昂贵的工具机,认为EUV在2017年开始试产的7nm制程将大发神威,成为主力机种。全球每年生产上百亿片的手机晶片、记忆体,数十年来都仰赖程序繁琐,但原理与冲洗照片类似的曝光显影制程生产。其中以投射出电路图案的微影机台最关键、也最昂贵。

过去十多年,全球最先进的微影机,都采用深紫外光,然而英特尔、台积电量产的最先进电晶体,大小已细小到仅有10 nm左右。而波长仅有13nm的EUV,依照该技术的主要推动者英特尔规划,2005年就该上阵,量产时程却一延再延。主要是因为这个技术实在太难了。EUV光线的能量、破坏性极高,制程的所有零件、材料,样样挑战人类工艺的极限。例如,因为空气分子会干扰EUV光线,生产过程得在真空环境。而且,机械的动作得精确到误差仅以皮秒(兆分之一秒)计。

最关键零件之一,由德国蔡司生产的反射镜得做到史无前例的完美无瑕,瑕疵大小仅能以皮米计。因为EUV的技术难度、需要的投资金额太高,另外两大微影设备厂──日本的Nikon和佳能,都已放弃开发。

各企业正破解难题,攻克EUV技术缺陷

ASML俨然成为半导体业能否继续冲刺下一代先进制程,开发出更省电、运算速度更快的晶圆体的最后希望。因此,三年前,才会出现让ASML声名大噪的惊天交易。

英特尔、台积电、三星等彼此竞争的三大巨头,竟联袂投资ASML41亿、8.38亿、5.03亿欧元。(台积电已于今年五月出售ASML的5%持股,获利214亿台币)于是,ASML研发经费倍增到现在的每年十三亿欧元的规模。多出的一倍,ASML自己出一半,三大半导体巨头合出另一半。

前英特尔(Intel)微影技术专家Yan Borodovsky预期,业界工程师应该能够使用EUV步进机进行2-3次曝光,打造出5nm或甚至是3nm组件。随着芯片缺陷的不断上升,最终将迫使工程师们采用新的容错处理器架构,例如神经网络。

最近的缺陷突然出现在15nm左右的关键尺寸上,而这是针对2020年代工工艺制造5nm芯片所需的技术节点。因此EUV制造商ASML也正在准备可印制更精细几何尺寸的下一代EUV系统,但这些系统预计要到2024年之后才会推出。