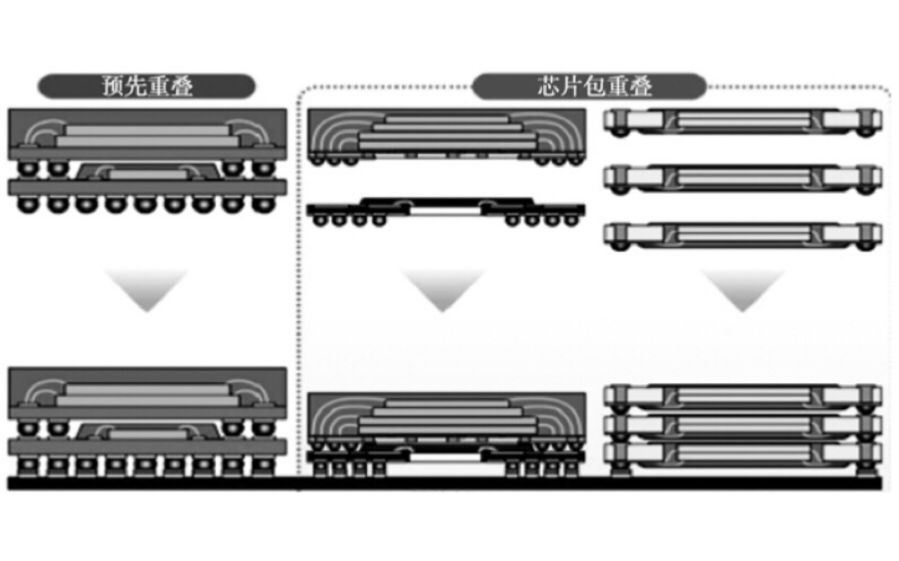

③ MCM:20世纪90年代初随着LSI设计技术和工艺技术的进步,以及深亚微米技术和微细化芯片尺寸等技术的应用,即将多个LSI芯片组装在一个多层布线的外壳内,形成了MCM多芯片封装器件。近年来,MCM技术通过FOP(堆叠封装)的形式,将2~4个裸片装在球栅阵列封装基板上,出现了多芯片模块(MCM),如图3所示。

图3

过去所说的MCM是指在一块基板上组装多个半导体芯片和元器件,近些年来半导体制造商开始由供应组装了多个芯片的存储器转向供应组装有多个芯片的SiP。SoC、SiP、MCM模组化微芯片技术的应用,导致了传统的电路设计技术发生了历史性的变革,设计和工艺的技术界限越来越模糊了。传统的电路设计技术功能越来越退化(未来的电路设计功能更多地是选用合适的芯片级功能模块及其接口类型),而微组装工艺技术却得到了极大的发展。未来电子装备的可靠性越来越取决于微电子组装工艺技术的发展。

例如:

●SiP使用的技术要素最基本的是CSP中所使用技术的组合。

●作为新加入的要素技术是芯片薄化加工技术、芯片积层技术、芯片积层中的互连技术。

●SiP安装形态目前包括:在印制板上平面配置芯片的形态(主要使用BGA),在印制板上直接积层芯片的形态(主要使用CSP),最近也使用了倒装芯片连接方式。

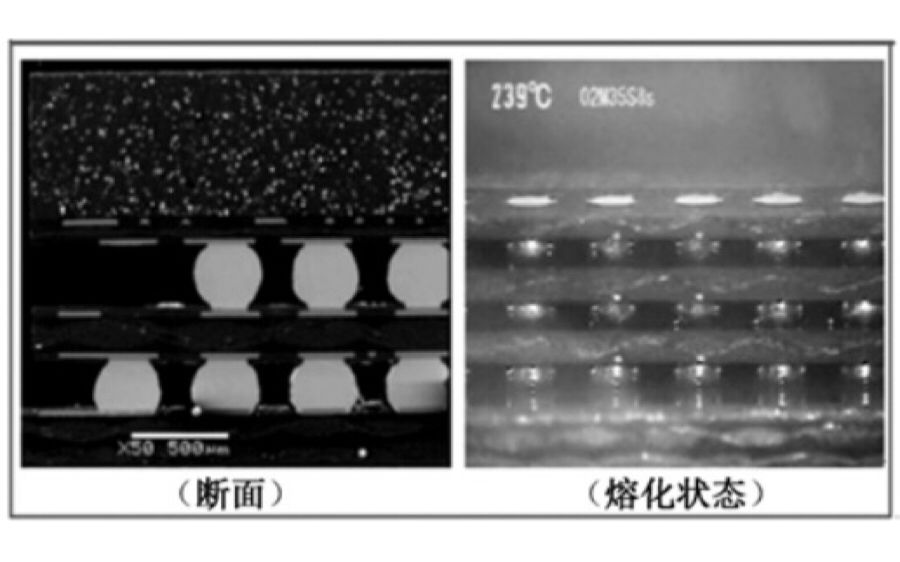

●芯片堆叠最具经济效益的是4~5个芯片的堆叠。“聚合物中芯片”工艺不采用金丝球焊,而是将芯片减薄后嵌入到薄膜或聚合物基中,如图4所示。

图4

(5)电子设备的安装密度不断增加。从第一代电子管进入第二代晶体管,后又从小、中规模集成电路进入到大规模和超大规模集成电路,电子产品正朝小型化、微型化,立体化封装方向发展。其结果导致装置安装密度的不断增加,从而使内部温升增高,散热条件恶化。而电子元器件将随环境温度的增高,降低其可靠性,因而元器件(特别是功率芯片)的可靠性引起了人们的极大重视。

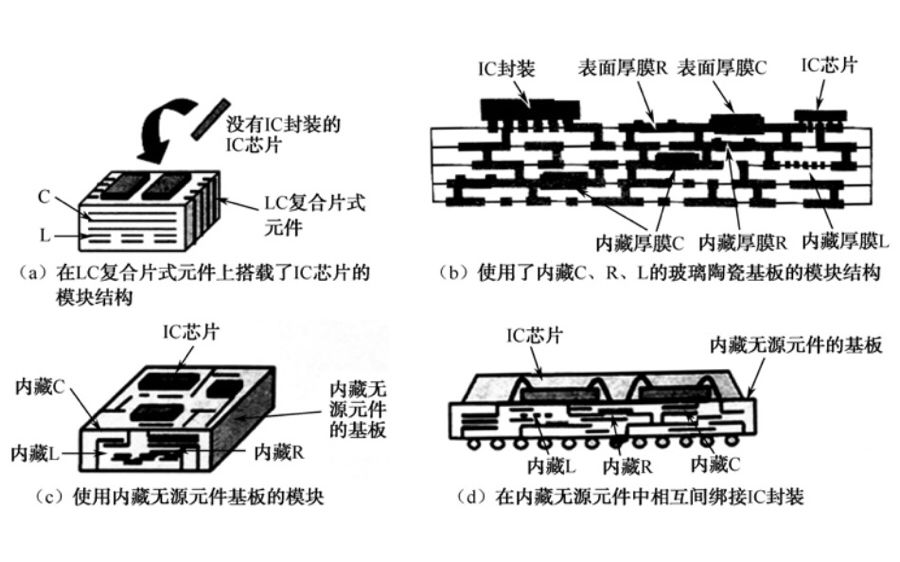

(6)将无源元件R、C、L(甚至IC裸芯)内藏于PCB基板中,然后再将未封装的IC芯片或IC封装贴装或绑接到内藏无源元件的基板表面,完成全部组装过程,如图5所示。

图5

HDI-PCB技术、内藏元器件基板技术,以及SoP、SiP及MCM等的结合,驱动了电子设备技术迈入了第五代。它改变了传统的由前决定后的串行组装模式,而迈入了前后并行的微组装模式的新时代。传统的产品可靠性管理和评估模式将面临着严重的挑战。由于有源和无源芯片封装的高集成化,系统安装的高密度化和立体化,焊接点的微细化和不可视化,导致了微组装工艺可靠性问题将变得异常突出。