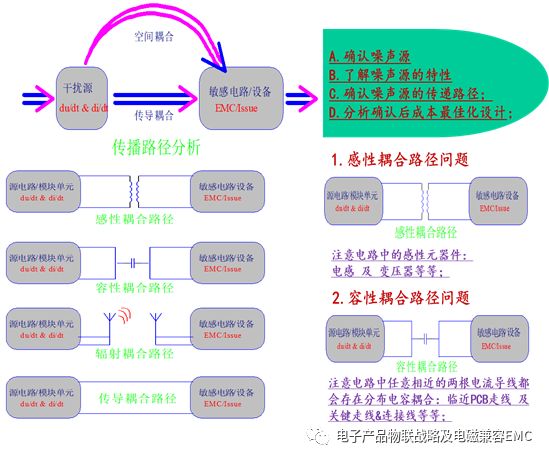

我们在谈到电子产品&设备的EMC问题的时候,EMC的三要素已经成为了我们的行动大纲;EMC三要素:干扰源-耦合路径-敏感设备;从理论上三要素如果解决处理好任意一个因素就构不成干扰或骚扰的问题;

EMC=EMI+EMS;对于EMS的三要素:干扰源(比如外部施加EFT,ESD,SURGE)通过传递路径(耦合路径)到我们的敏感电路产生噪声干扰;出现电子产品&设备的功能及性能的问题!

对于EMI的三要素:骚扰源(内部电路的du/dt(电压突变)&di/dt(电流突变))通过传递路径到等效天线的模型被我们的EMI的测试接收机接收;就形成了我们的EMI数据-必须达到无线电通信限值的要求!

我的EMI的理论是先分析再设计;实现性价比最优化原则!如下图:

通过上图我从EMI的正向设计进行了系统的讲述:对电子产品&设备首先;

A.确认有哪些噪声源;

B.分析噪声源的特性;相关资料可以通过网络搜索作者名字下载或观看;(我的理论:先分析再设计;了解噪声源头特性是关键)!

C.确认噪声源的传递路径;这也是我们大多数工程师处理EMI-Issue时的着手点;(处理的手段和方法);EMI的耦合路径:感性耦合;容性耦合;传导耦合;辐射耦合!

D.对上述的结果进行分析确认后;就会有最佳化的设计!

EMI骚扰的以下几种路径:(总的EMI的耦合路径进行分析)

对于空间耦合(辐射耦合)和传导耦合,大家都比较好理解;

辐射耦合:比如时钟源靠近端子连接线就会发生辐射耦合;

传导耦合:比如电子线路中有交叉的走线回路及关联线路就会发生传导耦合;

在实际中我们还有10%的EMI的问题也是众多设计师们没有注意的问题!从而要从PCB的分析来入手!!分析框图结构如下:

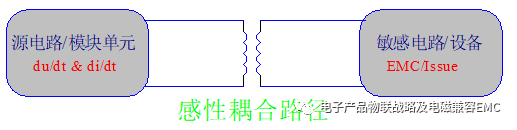

1.感性耦合路径问题

注意电路中的感性元件:

电感(输入&输出差模,共模电感,PFC电感,BUCK-L,BOOST-L…)及变压器等等;这些器件的位置放置及PCB走线都会带来EMI-Issue.

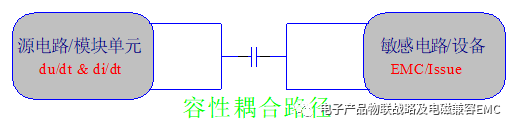

2.容性耦合路径问题

注意电路中任意相近的两根电流导线都会存在分布电容耦合:PCB走线 及 连接线等等;

我通过下面的原理分析框图来进行详细的说明;后面再给出我碰到的实际案例进行参考-分析电子产品&设备中的感性耦合与容性耦合问题;

上面的原理路径示意框图设计到的信息非常广,可以延伸到不同的电源拓扑结构;涉及到系统的传导理论,辐射理论;如果上面的电路你就当做是标准的PFC大功率应用电路;这时候你就会考虑30MHZ-300MHZ的骚扰功率的问题!如果电路结构前级输入是低压的交流输入(例如12VAC)这个电路可以是标准的升压(BOOST)电路结构;改变一下电感,开关MOS及输出二极管的位置;这个电路就可以变成高压或中低压的降压(BUCK)电路;也就是说这类电路的应用在EMI的问题表现及处理上都可使用同样的等效结构;处理EMI的问题就非常类同了。

A.在上面的电路结构中电感回路及输出回路比较优化,并且和交流输入有足够的距离时;如果有EMI的问题请参考《开关电源:EMC的分析与设计》快速设计理论方案!

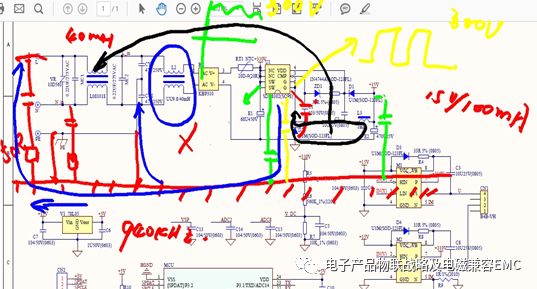

B.我在进行企业内训时就出现实际的特别案例;EMI传导设计-中高频部分优化我们共模滤波器没有明显的效果;分析框图结构如下:

该电路结构是典型的交流220VAC整流滤波后进行BUCK电路的高压降压电路设计,输出15V/0.1A 典型系统供电电路;EMI电路的滤波电路使用2级滤波器结构;我进行上述的EMI的路径分析这个2级滤波器完全足够解决150KHZ-10MHZ的传导干扰;进行分析如下:

1.检查PCB设计电路中的BUCK电感距离输入EMI滤波器较近;BUCK电路的高压电容的环路及续流二极管的环路面积均较大,且走线靠近输入滤波器走线!

由此分析如上图中黑线环路及路径造成了>940KHZ到几MHZ的EMI频段多点超标问题;(感性耦合-工字型电感 & 关键走线-容性耦合)

2.采用最简单的方式来判断问题;使用一个磁环将交流输入电源线绕3圈及以上;EMI超标点立刻消失并且通过EMI测试!

3.通过上面的磁环验证很明显我们找到解决问题的方法:去掉1级共模电感;使用一个双线并绕的共模电感(1-5mH均可)放置在电路板的电源线入口进行测试;整个EMI测试数据均达到10dB以上的裕量!