前言:

目前来看,Bizen可能会打开老式晶圆厂的逻辑生产之门。如果它能被业界采用,鉴于将给定技术节点上的Bizen裸片面积比CMOS逻辑实现的面积要小这一优势,或许能够将摩尔定律时钟倒退10年或更长时间。

传统晶体管面临重重压力

数十年来,芯片上的晶体管变得越来越小,越来越快,越来越便宜,可是近年来,摩尔定律正在面临失效。

更小、更快的新型晶体管将使得计算机工业再次取得巨大进步。通过这种方式,摩尔定律可能很快重新焕发生机,计算机性能有望迅猛增长。

晶体管日益发展,要突破物理极限,传统方法已经不适用,如今必须采用创新方法制造晶体管。

制程升级所面临现实难题

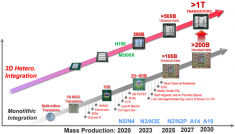

在过去,半导体市场的重点一直围绕着传统的芯片微缩,在器件中加入更多功能,然后在每个工艺节点上缩小器件。

然而到了最近几年,芯片在每个节点处的微缩都变得更加昂贵和复杂,如今只有少数人能够负担得起在先进节点上设计芯片的费用。

芯片行业对于数字的高度敏感,越来越成为晶圆代工厂商以及芯片厂商的紧箍咒。对于处于金字塔尖的巨头们来说,不无例外。

制程越先进,面积越小,性能提升的同时功耗也会降低,一般来说,10nm对16nm,功耗大约会下降20%到30%。数字越小则代表了越先进的技术水准。

但无论是芯片厂商还是晶圆代工厂商,越往升级道路走,承担的压力就越大。去年全球四大纯晶圆代工厂中,除了台积电,GlobalFoundries、联华电子和中芯国际每晶圆平均收入都在下降。

未来5年能有能力投入先进制程的晶圆代工厂,只有台积电、三星以及英特尔,激烈竞争之下,一定会让定价压力一路延烧到2022年为止。

传统结构的多元消耗

在多晶硅和栅极氧化物的界面处形成耗尽区,随着器件继续缩小,多晶硅耗尽变大,并且相当于氧化物厚度的较大部分将限制栅极氧化物电容。多元消耗的负面影响是由于反型层电荷密度的降低和器件性能的降低。

对于传统结构,随着沟道长度的缩小,栅极不能完全控制通道,这是不希望看到的。其影响之一是从漏极到源极引起更多的亚阈值泄漏,这从功耗角度来看不是很好,栅极不能控制远离其的泄漏路径,掺杂被插入通道中减少各种SCE。

新型量子遂穿晶体管诞生

英国晶圆代工厂Semefab生产了一种名为Bizen的新型量子隧穿晶体管和晶圆工艺样品,可以大大缩短交货时间、晶圆面积和工艺层,同时提高速度,降低功耗并提高CMOS的栅极密度。

Bizen是由位于英国诺丁汉的初创公司Search For The Next(SFN)开发的新型晶体管体系结构,其使用了量子隧穿而不是绝缘栅。这种结构由双极和齐纳二极管组合而成,它允许在标准CMOS工艺中仅在8层中产生逻辑,而对于传统CMOS晶体管设计,则需要20到30层。

Semefab在苏格兰Glenrothes生产的1μm制程工艺的Bizen测试芯片将传统CMOS晶体管设计的交货时间从15周缩短到了3周,并且芯片面积是同一工艺下同类CMOS器件的三分之一。

Bizen结构的本质和应用

Bizen是一种新颖的晶体管结构,本质上是一种PNP器件,其基极通过量子隧道结驱动,并且包括第二个隧道结内部的自偏置晶体管。目前,这种结构是基于硅的,但是能够迁移到GaN和其他化合物半导体。

量子隧穿技术并不是什么新鲜事物,它已被广泛应用于NOR闪存芯片中。但是,在过去的两年中,借助Bizen该技术已应用于逻辑器件,并已由Semefab进行生产、验证。

通过仔细建模,可以将传统的横向和纵向双极结构集成在一起,以整合成Bizen,而不会造成额外的工艺复杂性,可见它的确具有颠覆该行业的潜质。

尽管CMOS容易发生闩锁和ESD,但是否有缺陷对CMOS来说并不是什么大问题,而且CMOS的低功耗特性,已经通过了时间的考验,并且普遍可靠。

但是CMOS比较复杂,并且与功率集成时更是如此,复杂性意味着更长的交货时间和更高的成本,而Bizen恰好能够解决这些问题。