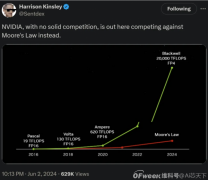

在摩尔定律的指引下,芯片上集成的晶体管数量不断超越人们的想象,芯片性能也不断升级,同时成本逐年下降。

但随着半导体制造工艺的不断升级,从7nm、5nm到3nm等延伸下去,越来越接近物理极限,而工艺提升所带来的成本效益也越来越不明显,仅靠工艺节点提升已无法满足市场需求。如何让芯片继续提升算力同时降低成本?业界需要在其他途径上再想对策。

Chiplet芯粒技术就是一个新的探索。

日前,在IC CHINA 2020的开幕式上,芯原股份创始人、董事长兼总裁戴伟民详细解读了Chiplet芯粒这一新技术,剖析了Chiplet时下的新机遇。

Chiplet最早由Marvell创始人周秀文提出,在ISSCC2015上,周秀文率先提出MoChi(Modular Chip,模块化芯片)架构的概念。据戴伟民介绍,MoChi是许多应用的基准架构,包括物联网、智能电视、智能手机、服务器、笔记本电脑、存储设备等。

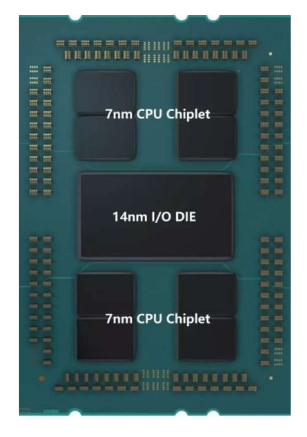

戴伟民认为,先进工艺中只有22nm、12nm和5nm这三个工艺节点是“长命节点”,其他中间节点的“寿命”都比较短。而且,并非每种芯片都需要5nm这样的尖端工艺,因为不是每一家公司都能负担起5nm工艺的成本,于是Chiplet这种将不同工艺节点的die混封的新形态是未来芯片的重要趋势之一。

据戴伟民介绍,目前将Chiplet运用做得最好的是AMD。在一块芯片上,CPU用的是7nm工艺,I/0则使用的是14nm工艺,与完全由7nm打造的芯片相比成本大约降低了50%。

“AMD是最会做大芯片的公司,连它都能接受小芯片,这很好的证明了Chiplet的发展前景。”戴伟民表示。

戴伟民在演讲中还特别强调,封装和接口对于Chiplet的重要性。台积电的CoWoS技术和英特尔的Foveros 3D立体封装技术都为Chiplet的发展奠定了基础,接口则代表了标准问题,芯片拼接在一起需要有一致的互联协议。所以,戴伟民表示,何时切入Chiplet领域很关键,如果过早切入,则没有标准可以依靠,设计好的成品可能会面临日后的接口不匹配等问题。

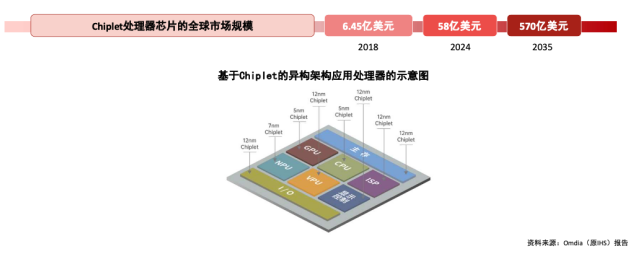

不过,整体来看,Chiplet给半导体全产业链都带来了新的机会。戴伟民指出,芯片设计环节能够降低大规模芯片设计的门槛;半导体IP授权商能升级为Chiplet供应商,提升IP的价值且有效降低芯片客户的设计成本;芯片制造与封装环节能够增设多芯片模块(Multi-Chip Module,MCM)业务,Chiplet迭代周期远低于ASIC,可提升晶圆厂和封装厂的产线利用率;标准与生态环节,则能够建立起新的可互操作的组件、互连、协议和软件生态系统。例如,作为IP供应商的芯原提出了IP as a Chip(IaaC)的理念,旨在以Chiplet实现特殊功能IP从软到硬的“即插即用” ,解决7nm、5nm及以下工艺中性能与成本的平衡,并降低较大规模芯片的设计时间和风险。

据Omdia报告,2018年Chiplet市场规模为6.45亿美元,预计到2024年会达到58亿美元,2035年则超过570亿美元,Chiplet的全球市场规模正在井喷式增长。