3.4 顶层

3.5 仿真

本次仿真使用到了task语句,task语句通常在当仿真时需要给输入变量特定的输入值时使用,例如本次仿真对rx端进行赋值。

3.6 仿真结果及问题排查

Rx端:

整体波形如图:

查看细节如下:

当rx=1时,输出的o_data并行数据在o_flag = 1(即表示传输结束)时也为1,结果正常。

Tx端:

整体波形如下:

上图很明显可以看出tx端传输有问题,当tx发送起始位(即拉低)后,没有将数据输出。观测其他信号波形,基本正常。可见问题大概率出现在tx赋值部分,一开始以为是发送数据位的条件判断有问题,检查代码,数据传输时的判断条件如下:

查看波形发现该条件可以被满足。

后来查看起始位的发送条件时发现了错误:

起始位发送要与tx_en同步。假设条件使用tx_en判断,则会比tx_en慢一拍。

另外,不能使用tx_en == 1'b1作为发送起始位的判断条件,因为tx_en 在数据发送时一直为1,这样tx端会恒为0,修改后代码如下:

再观察波形正常。

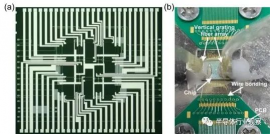

3.7 上板最终效果

代码下载进开发板后,在串口调试助手中可以正常收发数据,如下:

文章来源:润欣科技Fortune微信公众号