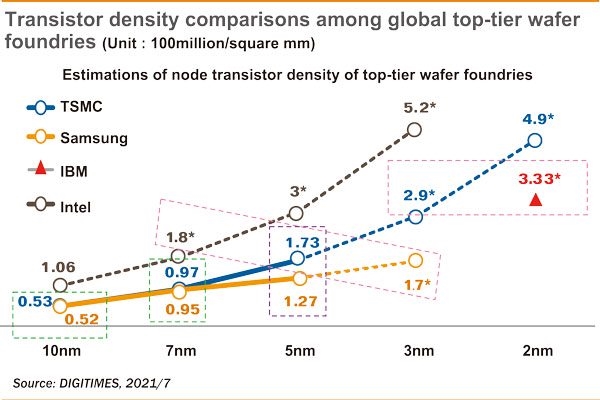

近日,Digitimes发布的一份研究报告中,详细分析了台积电、三星、Intel及IBM四家厂商在相同命名的半导体制程工艺节点上的晶体管密度问题,并对比了各家在10nm、7nm、5nm、3nm及2nm的晶体管密度情况。

(数据源自Digitimes)

10nm

在10nm节点,三星的晶体管密度只有0.52亿个/mm2,台积电是0.53亿个/mm2,英特尔已经达到了1.06亿个/mm2。英特尔的晶体管密度达到了台积电和三星的两倍左右。

7nm

在7nm节点,三星的晶体管密度是0.95亿个/mm2,台积电是0.97亿个/mm2,而英特尔预计将达到了1.8亿个/mm2。英特尔的晶体管密度依然比台积电和三星高出了80%以上。

5nm

在5nm节点上,三星的晶体管密度提升到了1.27亿个/mm2,台积电则达到了1.73亿个/mm2,英特尔将达到3亿个/mm2。英特尔的晶体管密度比台积电高出了超过73%,达到了三星2.36倍。

3nm

到了3nm节点,台积电的晶体管密度大约是2.9亿个/mm22,三星只有1.7亿个/mm2,英特尔将达到5.2亿个/mm2。英特尔的晶体管密度比台积电高出了超过79%,达到了三星2倍以上。即便是英特尔的5nm制程,其晶体管密度也达到了三星2nm的1.76倍。

2nm

至于2nm节点,目前没多少数据,IBM之前联合三星等公司发布的2nm工艺密度大约是3.33亿个/mm2,台积电的目标则是4.9亿个/mm2,均低于英特尔3nm的晶体管密度。

虽然以上数据其实不能100%反映各家的工艺技术水平,因为还需要考虑到其他的例如鳍片间距、栅极间距、最小金属间距、逻辑单元高度、功耗、成本等方面的问题。但就摩尔定律关注的晶体管密度指标来看,在同一制程工艺节点上,英特尔的优势巨大,甚至相比台积电、三星更新一代的制程工艺也同样具有一定的领先优势。