近一年来,半导体需求不断增加,与此同时,疫情导致海外厂商供应链失衡。“缺芯”潮下,产业发展的高景气度有增无减。据了解,国内半导体封装规模增速高于全球,先进封装未来增速将更高。

一、封装规模:受益于半导体产业向大陆转移,国内封测市场增速高于全球

封测分为封装环节和测试环节,根据Gartner统计,封装环节价值占封测比例约为80%-85%,测试环节价值占比约15%-20%。

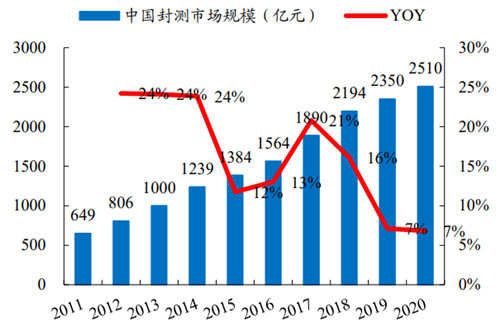

全球封测市场规模稳定增长,国内封测市场增速高于全球。据Yole数据,全球封测市场规模保持平稳增长,2020年达594亿美元,同比+5.3%。受益于半导体产业向大陆转移,国内封测市场高速发展,增速显著高于全球,据中国半导体行业协会数据,2020年国内封测行业市场规模达2510亿元,同比+6.8%,2016年至2020年CAGR约12.5%。

图:2020年全球封测行业市场规模预计同比+5.3%

图:2020年中国封测规模达2510亿元,同比+6.8%

二、芯片发展进入后摩尔时代,先进封装已成为提升电子系统及性能的关键环节

据英特尔知名人士分析,集成电路上可以容纳的晶体管数目在大约每经过18个月便会增加一倍。换言之,处理器的性能每隔两年会翻一倍。

然而近些年,随着芯片工艺不断演进,硅的工艺发展趋近于其物理瓶颈,晶体管再变小变得愈加困难:

一方面,技术难度迅速加大。在2011年以前,传统晶体管结构都是平面的,传统平面晶体管结构随着制程升级漏电等缺陷越发明显,因此英特尔自22nm,三星和台积电分别从14nm和16nm制程节点时期引入FinFET(鳍式场效应晶体管)技术,一直沿用到目前最先进的5nm制程。然而再往下的制程时,FinFET技术也遇到了瓶颈,晶圆厂将使用GAAFET(Gate-All-Around,闸极环绕场效应晶体管)等新技术,GAAFET是更加立体和复杂的3D晶体管,因此难度更高。同时由于“一代设备,一代工艺”,对于决定制程突破关键的上游设备厂商来说,难度也进一步加大,以光刻机为例,ASML是全球唯一有能力制造EUV光刻机的厂商,而面向3nm及更先进的工艺,晶圆厂将需要一种称为高数值孔径(high-NA)EUV的新技术,据ASML年报披露,正在研发的下一代采用high-NA技术光刻机要等到2024年才能量产。

另一方面,由于随着技术节点的不断缩小,集成电路制造设备的资本投入越来越高,仅有少数几家晶圆龙头有能力继续往先进制程突破。制程越先进,生产技术与制造工序越复杂,制造成本呈指数级上升趋势。例如当技术节点向5nm甚至更小的方向升级时,普通光刻机受其波长的限制,其精度已无法满足工艺要求,需要采用昂贵的EUV光刻机,1台EUV价格约14亿元。或者采用多重模板工艺,重复多次薄膜沉积和刻蚀工序以实现更小的线宽,使得薄膜沉积和刻蚀次数显著增加,意味着需要更多的光刻机、刻蚀和薄膜沉积等设备。以5nm节点为例,设备支出高达31亿美元,是14nm纳米的2倍以上,28nm的4倍左右。

图:随着技术节点升级,集成电路制造的设备投入呈大幅上升的趋势

因上述原因,摩尔定律逐渐放缓,后摩尔时代到来,先进封装因能同时提高产品功能和降低成本是后摩尔时代的主流发展方向。半导体封装技术发展大致分为四个阶段,全球封装技术的主流处于第三代的成熟期,主要是CSP、BGA封装技术,目前封测行业正在从传统封装(SOT、QFN、BGA等)向先进封装(FC、FIWLP、FOWLP、TSV、SIP等)转型。

先进封装与传统封装以是否焊线来区分,先进封装主要有倒装芯片(FC)结构的封装、晶圆级封装(WLP)、2.5D封装、3D封装等。分为两个方向:(1)小型化:3D封装突破传统的平面封装的概念,通过单个封装体内多次堆叠,实现了存储容量的倍增,进而提高芯片面积与封装面积的比值。(2)高集成:系统级封装SiP能将数字和非数字功能、硅和非硅材料、CMOS和非CMOS电路以及光电、MEMS、生物芯片等器件集成在一个封装内,在不单纯依赖半导体工艺缩小的情况下,提高集成度,以实现终端电子产品的轻薄短小、低功耗等功能,同时降低厂商成本。

图:传统封装向倒装芯片、晶圆级封装演进

在5G、消费电子、物联网、人工智能和高性能计算等更高集成度的广泛需求下,先进封装市场增速预计将高于传统封装。据Yole数据及预计,全球先进封装市场规模2024年预计近440亿美元,2018-2024年CAGR预计达8.2%。而在同一时期,传统封装市场规模CAGR预计仅为2.4%,整个IC封装产业市场规模预计CAGR为5%。

作者:我爱方案网整理来源:我爱方案网