最近市场传言,芯片设计公司AMD将成为三星代工厂的第一个3nm客户。中国台湾DigiTimes的消息人士认为,由于台积电与苹果的密切关系使得AMD考虑选择三星进行3nm订单,并且同AMD一样,高通也对三星的3nm制程感兴趣。

3nm工艺对抗赛逐渐形成

苹果与台积电和合作已经长达十年,截止目前苹果仍然是台积电最大的客户,占台积电2020年480.8亿美元总营收的四分之一。据台积电的一份客户订单数据显示,2020年苹果获得了台积电产能的24.2%,2021年这一数字已达到25.4%。

在苹果最新发布的芯片线路图中,苹果预期在2023年发布基于3nm的第三代M系列芯片,并且依旧选择了台积电代工3nm制程。

台积电与苹果早已形成稳定的合作关系,而在考虑产能问题的AMD、高通极有可能与三星合作。

此前,由于台积电在7nm及5nm工艺上占据优势,台积电的客户数量及订单都远高于三星,苹果、高通、AMD都是其客户。凭借着优良的5nm工艺,台积电可以说是横扫天下。

但因为在7nm、5nm上竞争不足,三星选择另辟蹊径,将重点押注在3nm节点上。不仅在3nm上选择了GAA晶体管技术,合作伙伴上也取得了突破。在前两天的的三星先进代工系统论坛会上,三星官方宣布已有12家合作伙伴深入合作。当传出高通与AMD有意合作的消息后,更像是在三星3nm的布局上添上的一把火。

如今3nm工艺对抗赛逐渐形成,3nm之战一触即发。

3nm的决战

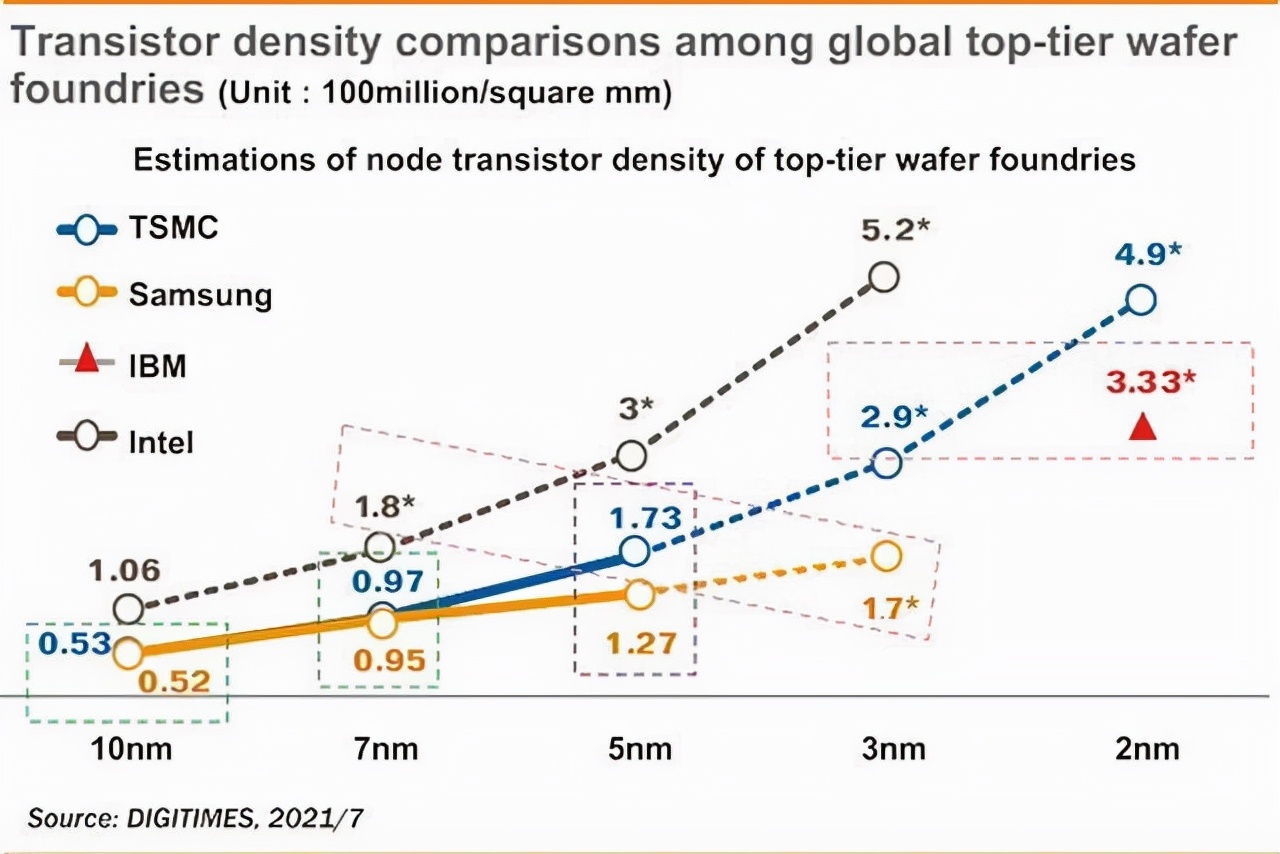

在半导体制程的进程中,3nm工艺是继5nm 技术之后的下一个工艺节点。晶圆制造三巨头中台积电、三星、都宣布了其3nm的研发和量产计划,而英特尔则更改了节点的度量方式,采用PPA的方式进行制程节点划分。需要注意的是,研究报告曾指出,英特尔的Intel 3(此前称5nm制程)的晶体管密度达到了三星2nm的1.76倍。量产时间节点与晶体管密度指标的比拼,使得3nm制程的对抗赛越发有看头。

3nm制程节点正在上演“三英战吕布”的戏码,明年上半年将要量产的三星3nm、明年下半年将要量产的台积电3nm、2023年下半年才会亮相的Intel 3,谁才能优先取得优势?

台积电

从时间节点来看,台积电的3nm制程布局时间要早于三星。在2016年,台积电就计划建设一个5nm至3nm节点的晶圆制造厂;在2017年,台积电宣布在中国台湾台南科学园开始建设3纳米半导体制造厂。

去年8月,台积电发布了其N3 3nm工艺的细节。此节点可提供比N5更完整的扩展能力,性能提升10-15%,功耗降低25-30%,密度提高70%。台积电计划在2021年进行风险生产。

而工艺的选择上,台积电的3nm芯片选择了增强的Fin FET(鳍式场效应晶体管)技术,SRAM密度增加20%,模拟密度增加10%。

今年4月,针对三星的2030蓝图计划,台积电也明确放话,今年资本支出维持原定的150亿~160亿美元,并全力冲刺延用鳍式场效电晶体(Fin FET)技术的5nm、3nm制程,预计2022年下半年量产。

三星

自2017年,三星正式宣布调整公司业务部门,将晶圆代工业务部门从系统LSI业务部门独立出来,成立三星电子晶圆代工厂,负责为全球客户制造逻辑芯片时,三星在晶圆代工上的赛道上算是正式参赛。

想在3nm上扳回一局的三星,不但在时间上拔得头筹,提前台积电半年量产;还采用了全新的GAAFET技术(全环绕栅极晶体管工艺)。

因为GAA技术重新设计晶体管底层结构,克服了当前技术的物理、性能极限,增强栅极控制,使得性能大大提升。

在该技术方向下,主要有纳米线、板片状结构多路桥接鳍片、六角形截面纳米线和纳米环技术四大主流方向,三星采用的是MBCFET(Multi-Bridge Channel FET),即板片状结构多路桥接鳍片。

在IEEE国际固态电路会议上,三星工程师展示了其MBCFET结构的灵活性。如何以极低的电压实现片上存储单元的写入操作,其电压可以降低数百毫伏,从而有可能大大降低未来芯片的功耗。

与5nm工艺相比,采用MBCFET晶体管结构,其面积减少了35%,性能提高了30%且功耗降低了50%。三星电子总裁兼代工业务负责人Siyoung Choi称,随着工艺成熟度的提高,三星电子3nm工艺良率正在接近目前量产的4nm工艺水平。

在三星的最新计划中,将在韩国扩建紫外光(EUV)光刻技术生产线,该技术使用波长13.5nm的极紫外光,能够制造出更精细、更清晰的电路,从而让芯片搭载更多元件,大幅度提升运算能力与效率。

英特尔

在3nm制程的布局上,英特尔同样布局。英特尔为其制程节点引入了全新的命名体系,市面上来说,Intel 3相当于其他厂商的3nm制程。

关于Intel 3的消息,目前不算太多。根据英特尔的制程路线图来看,Intel 3会在Intel 4之后亮相。不久前,英特尔刚公开了Intel 4的进程,表示将会第一次引入EUV光刻机,明年下半年投产,2023年产品上市。其官方网站还公开了48秒的视频,表明该加工工艺生产的晶圆检测过程,并且得出了最终的结论。根据全部检测,内部的SRAM、逻辑单元、模拟单元都符合要求,处理芯片很“健康”。

在“英特尔加速创新”线上发布会上,英特尔计划Intel 3 将在2023年下半年亮相,预计是Intel 4即7nm工艺的升级技术,同样使用Fin FET晶体管,每瓦性能将提升约18%。但没有具体的发布时间或产品名称,推测将于2024年上市。

对于GAA技术的布局,英特尔则会在20A(Intel 20A 中的 A 代表单位“埃格斯特朗”?ngstr?m,简称埃,符号?,是一种小于纳米的测量单位。1A = 0.1nm)工艺上使用,并且将兼备RibbonFET和PowerVia两大突破性技术。

其实,就摩尔定律关注的晶体管密度指标来看,在同一制程工艺节点上,英特尔的优势巨大。在Digitimes发布的一份研究报告,分析了台积电、三星、Intel在相同命名的半导体制程工艺节点上的晶体管密度问题。报告中,在3nm的节点上,台积电的晶体管密度大约是2.9亿个/mm2,三星只有1.7亿个/mm2,英特尔将达到5.2亿个/mm2。英特尔的晶体管密度比台积电高出了超过79%,达到了三星2倍以上。

3nm工艺进程受阻

不久前,The Information报导,台积电3纳米制程陷入瓶颈,可能会导致iPhone处理器连续三年(包括明年)都卡在同一制程,为苹果史上首见。对此,台积电则重申,3纳米制程按计划进行,不评论客户或市场传闻。

但这不是外界第一次传闻台积电3nm制程延期。在今年9月初,台积电曾正式确认,3nm工艺的量产会延迟3到4个月。

值得注意的是,虽然在今年上半年三星宣布其3nmGAA工艺已经成功流片,但是在三星代工论坛活动上,三星表示转移到全新的GAA技术难度很高。相对于曾经计划在2021年下半年量产芯片,三星将3nm制程延期到2022年。最近,也有路透社消息称三星电子的3nmGAA工艺目前仍面临着漏电等关键技术问题。

虽然对于外界的传闻,三星与台积电都不置可否。但从纷纷流言中可以看出,3nm工艺的落地并不是一件简单的事。

3nm工艺究竟难在什么地方?

实际上,每次遵从摩尔定律的提升,都需要一个关键技术。

这十年间,比较著名的关键技术就是HKMG和Fin FET了,HKMG是Intel在45nm节点引入的,可以用于改善传统二氧化硅绝缘层的漏电,随后Intel在22nm引入了Fin FET来加强栅极的控制能力。但随着芯片制程越来越小,到了3nm的节点,不同厂商对于使用何种工艺有不同的判断。

随着工艺的进展,在5nm之后,Fin FET会遇到很多问题。其不断拉高的深度和宽度之比(为了避免短沟道效应,鳍片的宽度应该小于栅极长度的0.7倍),将使得鳍片难以在本身材料内部应力的作用下维持直立形态,尤其是在能量更高的EUV制程导入之后,这样的状况会更为严重,甚至光子在如此小的尺度下将呈现量子效应从而带来大量的曝光噪音,严重影响了产品的质量和性能。另外,栅极距过小将带来不可控的情况。

但这并不代表着5nm后,不会出现采用Fin FET工艺的3nm芯片。

在综合性能、成本等因素后,台积电选择在3nm上采用Fin FET工艺。在技术大会上,台积电还表示,已经对Fin FET技术进行了重大更新,通过其工艺节点技术的另一次迭代实现性能和漏电扩展,有自信能在3nm节点以Fin FET来获得水准之上的良率。

就目前而言,Fin FET工艺还有大约3倍密度的生命力空间,也就是在密度300MTr附近Fin FET依旧是可用的,台积电最后的Fin FET工艺N3在保持Fin FET的情况下做到了250MTr/mm2的密度,到达Fin FET的极限。在2nm工艺节点,台积电将转为GAA工艺。

三星则认为Fin FET在5nm和4nm工艺节点上都依旧有效,而在3nm时代三星开始使用新的GAA技术。希望在这个节点上超越台积电。在密度上,基于GAA大约可以实现密度的再次范围,到达600MTr的密度(累计6倍)。并且三星使用的MBCFET技术,与目前采用纳米线来构造晶体管技术不同。三星MBCFET使用纳米片构造晶体管,以增加与闸极的接触面积,进而让装置整合更简单,同时增加电流。

写在最后

无论选择那种工艺,3nm制程必然都是困难的。3nm的对抗赛还在继续,不到市场正式出现3nm制程芯片,一切都只是暗潮汹涌。

如果三星靠3nm扳回一局,那么全球的芯片将再次迎来新变局,台积电的选择是否能守住代工一哥的擂台,英特尔能借着Intel 3重回巅峰吗?

3nm的决战已经正式开始。