2021 IEEE国际电子器件会议(IEDM)上,“蓝色巨人”IBM联合三星共同推出“垂直传输场效应晶体管”(VTFET) 芯片设计新工艺。

(资料图)

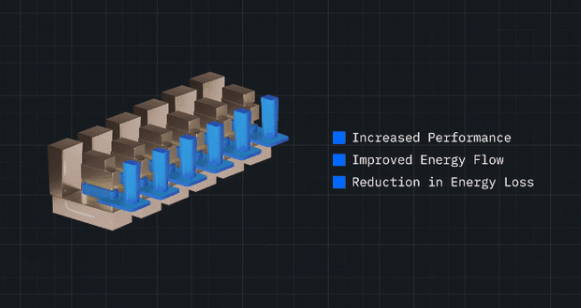

IBM与三星将晶体管以垂直方式堆叠,并让电流也垂直流通,使晶体管数量密度再次提高,更大幅提高电源使用效率,并突破1nm制程的瓶颈。

相较传统的水平放置晶体管的设计,这种新型的垂直传输场效应晶体管将能增加晶体管数量堆叠密度,在每个芯片上实现更高密度的这些组件,让运算速度提升两倍,同时借电流垂直流通,使功耗在相同性能发挥下降低85%。通过这种新设计,IBM和三星希望将摩尔定律扩展到纳米片阈值之外并减少能源浪费。

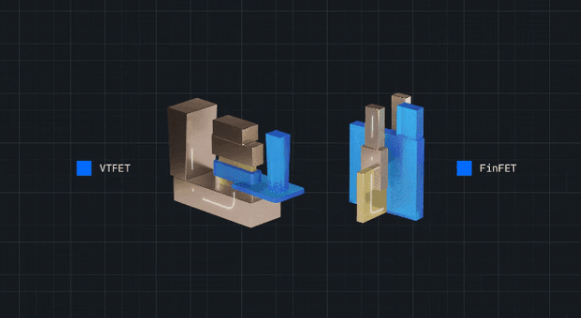

(接通电流时,VTFET(和横向 FinFET晶体管组合结构的并排比较)

此外,IBM和三星还指出,此技术用在未来手机上以后,一次充电续航时间可长达一星期,可使某些耗能密集型任务如加密运算更省电,减少对环境的影响。不过IBM与三星尚未透露何时开始将垂直传输场效应晶体管设计应用于产品,但是市场人士预估,短时间内会有进一步消息。

IBM 研究院混合云和系统副总裁 Mukesh Khare 博士表示:“今天我们共同发布这项新技术是在致力于挑战突破传统思路,重新思考我们应该如何持续推动社会进步,并提供新的创新,以改善人类的生活、工作和减少对环境所带来的负面影响。”

当今,主流的芯片架构采用的是横向传输场效应晶体管(FET),例如鳍式场效应晶体管(FinFET),因硅体类似鱼背鳍而得名。随着摩尔定律的延续,集成电路上可以容纳的晶体管数目在大约每经过18个月便会增加一倍,同时计算机的运行速度和存储容量也翻一番,如今可以塞进单个芯片的晶体管数量也几乎达到了极限。全新的设计方法能通过放宽晶体管门长度、间隔厚度和触点尺寸的物理限制来解决缩放(scaling )障碍,并在性能和能耗方面对这些功能进行优化,这或许或成为未来芯片设计的新方向之一。