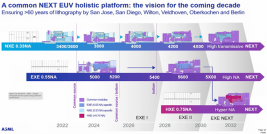

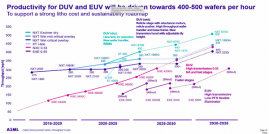

ASML已经向Intel交付第一台高NA EUV极紫外光刻机,将用于2nm工艺以下芯片的制造,台积电、三星未来也会陆续接收,可直达1nm工艺左右。

那么之后呢?消息称,ASML正在研究下一代Hyper NA(超级NA)光刻机,继续延续摩尔定律。

ASML第一代Low NA EUV光刻机只有0.33 NA(孔径数值),临界尺寸(CD)为13.5nm,最小金属间距为26nm,单次曝光下的内连接间距约为25-30nm,适合制造4/5nm工艺。

使用双重曝光,可将内连接间距缩小到21-24nm,就能制造3nm工艺了,比如台积电N3B。

第二代EUV光刻机提高到了0.55 NA,临界尺寸缩小到8nm,金属间距最小约为16nm,可制造3-1nm,比如Intel就透露会在1.4nm节点上首次使用。

ASML CTO Martin van den Brink在接受采访时确认,ASML正在调查开发Hyper NA技术,继续推进各项光刻指标,其中NA数值将超过0.7,预计在2030年左右完成。

它表示,这种新型EUV光刻机适合制造逻辑处理器芯片,相比高NA双重曝光成本更低,也可用来制造DRAM内存芯片。

ASML已披露的数据显示,低NA光刻机的成本至少1.83亿美元,高NA光刻机更是3.8亿美元起步。

根据微电子研究中心(IMEC)的路线图,2030年左右应该能推进到A7 0.7nm工艺,之后还有A5 0.5nm、A3 0.3nm、A2 0.2nm,但那得是2036年左右的事儿了。

按理说,美国是世界上最强大的国家,也有着最强大的半导体行业与技术,但现状不容乐观。

根据美国乔治城大学沃尔什外交学院智库CSET(安全和新兴技术中心)的最新报告,美国晶圆厂的建设速度几乎已经是全球最慢的,而中国大陆正在极速追赶上来。

报告显示,20世纪90年代以来,全球共新建了635座晶圆厂,平均建设时间为682天。

建设速度最快的是日本,平均只需584天,然后是韩国620天、中国台湾654天、欧洲和中东690天、中国大陆701天。

美国则需要长达736天,只比东南亚的781天略好一些。

如果划分不同时间段来看,美国的情况更不容乐观。

199x年和200x年,美国平均只需675天就能建好一座晶圆厂,进入201x年则要花费918天。

与此同时,中国大陆和中国台湾分别缩短到了675天、642天。

进入202x年,美国的晶圆厂建设更是困难重重,经常无法按期完工。

比如台积电位于亚利桑那州的Fab 21又推迟了一年,Intel位于俄亥俄州的工厂从2025年延期到了2026年底,三星位于得克萨斯州的工厂跳票到了2025年。

数量方面美国也在快速下滑,199x年新建了55座,200x年只有43座,201x年则仅仅22座,合计120座。

同期,中国大陆分别新建了14座、75座、95座,合计184座,比美国多了足足一半。

虽然数量和速度不代表一切,尖端工艺上我们差距还非常大,但是CSET仍然提醒美国要小心中国的追赶。

尽管美国制定了《芯片法案》,推动半导体制造回流本土、抑制竞争,但效果不佳。

CSET强调,美国晶圆厂建设放缓,最大阻碍就是各种各样、纷繁复杂的法律法规,看似对公众有益,但严重阻碍了半导体发展,建议删除那些没必要的冗余条款,为半导体行业开绿灯。

建设中的Intel新工厂

原文标题 : ASML研究超级NA光刻机!2036年冲击0.2nm工艺