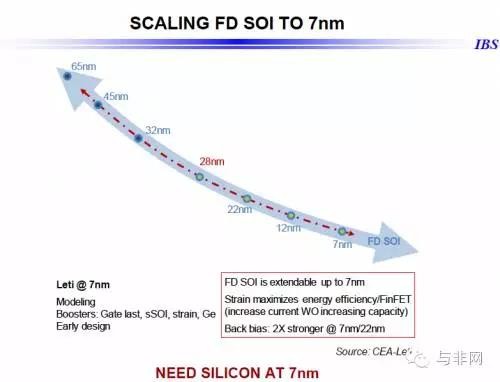

“多年以后我们写半导体发展史的话,28纳米节点一定是浓墨重彩的一笔,它背后有很多的故事。”在2016 FD-SOI论坛上,复旦微电子总工程师沈磊如是说。的确,28纳米以后逻辑工艺开始分岔:立体工艺FinFET由于获得英特尔与台积电的主推成为主流,14/16纳米都已量产,10纳米工艺也有可能在2017年量产;体硅工艺停止在28纳米,想增加集成度而又对FinFET开发成本望而却步的半导体公司另辟蹊径,开始考虑通过3D或者2.5D封装来延续摩尔定律;通过几年的发展,平面工艺FD-SOI生态链渐趋成熟,CEA-Leti的研究结果表明FD-SOI工艺至少可以延续到7纳米,这预示着FD-SOI不是一个孤节点工艺路线,设计公司与IP公司从观望转到介入,GlobalFoundries(格罗方德)表示目前有50余家设计公司在利用该公司的22纳米FD-SOI工艺进行设计。

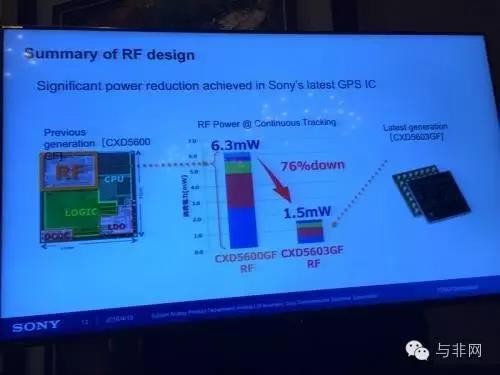

功耗性能比一向是FD-SOI工艺所强调的优势。根据三星提供的数据,相比体硅工艺(28纳米HKMG工艺),28纳米FD-SOI功耗相当于体硅工艺的70%,性能要高出16%。格罗方德将在2017年量产的22FDX(22纳米FD-SOI工艺)支持超低电压运行,只需0.4V电压就能够支持逻辑运算,与28纳米HKMG工艺相比,功耗降低了70%,漏电流只有约1pA/um。在此次论坛上引起热议的索尼GPS芯片CXD5600即采用28纳米FD-SOI工艺,由于在功耗方面的出色表现,已经被华米用于其新推出的AMAZFIT运动手表里面。

采用22FDX的GPS芯片将比现在的工艺更省电

格罗方德在此次论坛上发布12纳米FD-SOI工艺路线图,根据格罗方德的资料,这个被其称为“12FDX”的工艺可用16/14纳米FinFET成本实现10纳米FinFET性能。 而相比16/14纳米FinFET工艺,22FDX平台在设计规则和制造上具备更大的成本优势,例如,MOL设计规则22FDX比16/14纳米工艺减少 50%(总规则减少10~20%);无Fin-specific规则;减少曝光切割(约50%);更大器件套件(约2倍以上);最重要的是减少了40%的掩膜。

FD-SOI工艺可发展至7纳米