楷登电子(美国Cadence公司)近日宣布发布Cadence Sigrity 2018版本,该版本包含最新的3D解决方案,帮助PCB设计团队缩短设计周期的同时实现设计成本和性能的最优化。独有的3D设计及分析环境,完美集成了Sigrity工具与CadenceAllegro技术,较之于当前市场上依赖于第三方建模工具的产品,Sigrity 2018版本可提供效率更高、出错率更低的解决方案,大幅度缩短设计周期的同时、降低设计失误风险。 此外,全新的3D Workbench解决方案弥补了机械和电气领域之间的隔阂,产品开发团队自此能够实现跨多板信号的快速精准分析。

由于大量高速信号会穿越PCB边界,因此有效的信号完整性分析必须包括信号源、目标芯片、中间互连、以及包含连接器、电缆、插座等其它机械结构在内的返回路径分析。传统的分析技术为每个互连器件应用单独的模型后,再将这些模型在电路仿真工具中级联在一起,然而,由于3D分开建模的特性,从PCB到连接器的转换过程极易出错。此外,由于3D分开建模很可能产生信号完整性问题,在高速设计中,设计人员也希望从连接器到PCB、或是插座到PCB的转换过程可以得到优化。

全球PCB 打样服务商捷多邦了解到,Sigrity 2018最新版可帮助设计人员全面了解其系统,并将设计及分析扩展应用到影响高速互连优化的方方面面:不仅包括封装和电路板,还包括连接器和电缆领域。集成的3D设计及分析环境使PCB设计团队能够在Sigrity工具中实现PCB和IC封装高速互连的优化,然后在Allegro PCB、Allegro Package Designer或Allegro SiP Layout中自动执行已优化的PCB和IC封装互连,无需进行重新绘制。而直至今日,优化结果导回设计软件的流程始终是一项容易出错、需要仔细验证的手动工作。通过自动化该流程,Sigrity 2018最新版能够降低设计出错风险,免去设计人员花费数小时重新绘制和重新编辑工作的时间,更能避免在原型送到实验室之后才发现错误而浪费掉数天的时间。这不仅大大减少了原型迭代次数,更通过避免设计返工和设计延期而为设计项目节省大量的资金。

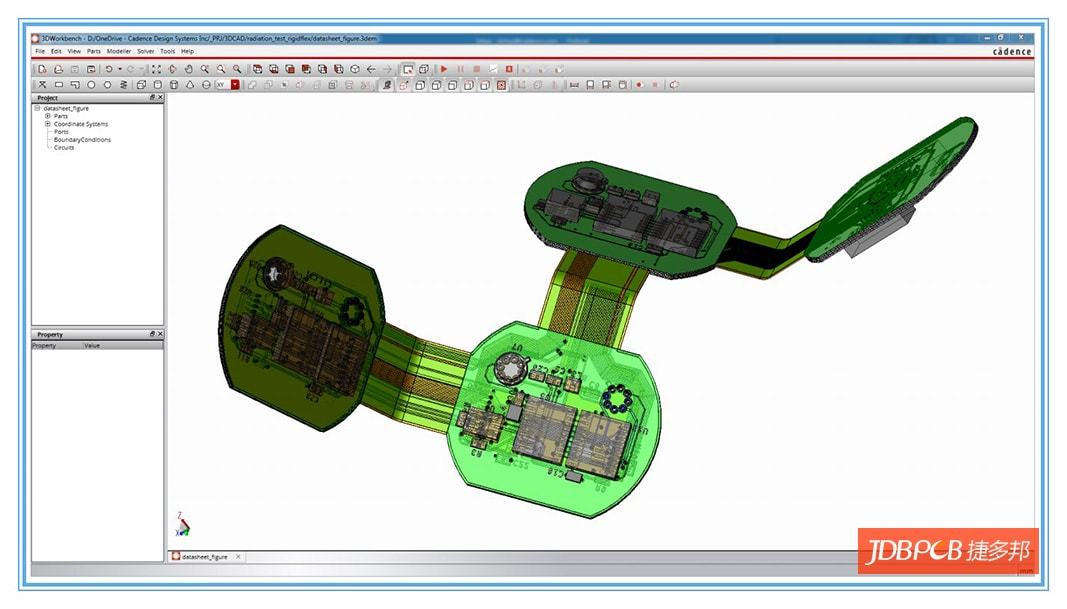

捷多邦获悉,Sigrity 2018最新版中的全新3D Workbench解决方案桥接了机械器件和PCB、IC封装的电子设计,从而将连接器、电缆、插座和PCB跳线作为同一模型,而无需再对板上的任何布线进行重复计算。 对互联模型实施分段处理,在信号更具2D特性且可预测的位置进行切断。通过仅在必要时执行3D提取、对其余结构则进行快速精准的2D混合求解器提取、再将所有互联模型重新拼接起来的方式,设计人员可实现跨多板信号的高效精确的端到端通道分析。

此外,据捷多邦了解,Sigrity 2018最新版为场求解器(如Sigrity PowerSI 技术)提供了Rigid-Flex技术支持,可对经过刚性PCB材料到柔性材料的高速信号进行稳健的信号分析。设计Rigid-Flex产品的团队现在可以运用以往仅限于刚性PCB设计的技术,在PCB制造和材料工艺不断发展的同时,开创分析实践的可持续性。

“在Lite-On,我们的存储器业务组(SBG)专注于固态磁盘企业数据中心的产品设计。 在极其密集的设计中考虑信号和电源的完整性问题变得越发重要,”Lite-On SBG研发主管Andy Hsu表示:“为了增强2D layout和3D连接器结构的集成,Lite-On SBG采用了包括Sigrity PowerSI 3D-EM和Sigrity 3D Workbench在内的Cadence 3D解决方案,该方案可支持无缝使用Cadence Allegro layout和Sigrity提取工具,从而显著缩短了我们的设计周期。 我们的工程师因此可以实现更加精准高效的仿真,并设计出以客户需求为导向的产品。”

“Sigrity 2018最新版通过紧密集成Cadence多个产品团队的技术,向前迈进了一大步,” Cadence公司资深副总裁兼定制IC和 PCB事业部总经理Tom Beckley表示:“通过整合Allegro和Sigrity团队的3D技术,我们不断完善客户的系统设计体验,帮助客户采取更全面的方法实现产品优化,不仅包括芯片、封装和电路板的优化,更包括机械结构的优化。”