EMC在电子产品/设备已经成为可靠性的重要组成部分;将越来越被重视!特别对于我们的工业&消费类产品要求满足其相应的认证和出口要求,对应的国家政策也在不断完善;同时国际贸易的深化发展;EMC技术成为电子产品/设备必过的硬性指标!

PCB 板的接口连接线及电缆的电磁兼容性(EMC)问题;分别来看EMI 和 EMS 这两个方面;

1.EMI-辐射发射的问题:

在下示意图中与电路板相连的电缆也是产生辐射问题的原因之一, 因为高速信号电流在电缆中流动由于环路和阻抗不匹配等原因;很易对外产生共模或差模的电磁辐射。

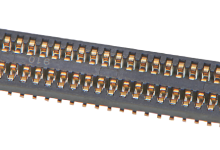

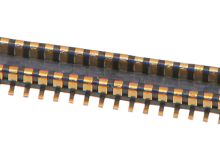

A.接口连接线(排线)

B.连接线缆

计算线缆的辐射强度时,将其等效为单极天线,其辐射强度由下式简化:

C.PCB走线:形成的差模环路和共模环路

PCB上有许多信号环路,其中有差模电流环也有共模电流环,计算其辐射强

度时,可等效为环天线,辐射强度由下式简化:

对比上面的公式可以看出连接线缆的辐射远大于 PCB 走线的辐射效率!

2.EMS-对于抗干扰问题:(EFT的设计问题)

注意:排线电缆对参考接地有分布电容;我们进行耦合群脉冲试验时;高频的干扰信号耦合进来了。这时候要检查GPIO控制的 输入接口要滤波(最简单用RC)和系统的供电的电源要进行干扰滤波;

案例:下面我的客户碰到问题:

(现在遇到一个问题;5V供电用线供电没有问题;但是用20pin的排线

会出现MCU停止工作的情况;好像晶振不起振了)

简单的判断思路:在长的连接线上绕了几个磁环能过EFT了!!确定问题;

改善方法:建议客户在PCB内部走线上先增加了两个磁珠 效果就非常明显!

客户的疑问:这个排线没有高速信号啊;排线(连接线)只有GPIO控制和5V电源;客户认为-会不会是地的原因?电源和地单点接电源板?然而排线只有控制信号!

进行分析排线对参考接地测试板有分布电容;在进行EFT试验时;高频的干扰信号耦合进来了。这时建议要检查GPIO控制的-输入接口要进行滤波(最简单用RC)和输入电源要进行干扰滤波; 而不是说这个排线有连接高速信号!才会出现问题;注意如果排线本身走高速信号;这时候就要考虑这个排线的EMI-辐射骚扰的测试问题了!如前面讲的EMI对外辐射发射的问题!

3.对于复杂的多层板或者双面板来讲通过PCB的屏蔽设计优化EMC:(重要!!)

A.为了减小电源的边缘辐射,电源/地平面应遵循20H 设计原则,即地平面尺寸比电源平面尺寸大20H;

B.电源走线两侧伴地而行;

C.关键器件及走线伴地而行;

D.关键走线时钟和射频信号线不能走PCB边缘布线!

4.排线及连接线的屏蔽化设计优化EMC:(重要!!!)

控制信号线是EMC干扰源的关键路径环节:

A.连接控制信号线是高速信号传输的关键环节,也是易产生EMI 的薄弱环节。

B.连接控制信号线也是EMS信号入口;连接到MCU/CPU的GPIO时需要增加阻抗器件(R,C,BEED,TVS等等!)

排线的屏蔽设计

A.采用带屏蔽线的设计-有条件

B.在连接器的端子设计上可多安排地针,减小信号与地的间距,关键信号需要两边伴地设计如上图示!

C.排线屏蔽设计,减小连接器中产生辐射的有效信号环路面积,提供低阻抗回流通路!

总结:

对于PCB板连接电缆的EMC问题的设计:

与电路板相连的排线电缆也是很容易耦合进来辐射问题的!因为高速信号电流在电缆中流动由于环路和阻抗不匹配等原因很容易产生对内&对外的电磁干扰。PCB连接线同时也是EMS信号入口;控制信号线连接到MCU/CPU的GPIO时需要增加阻抗器件(R,C,BEED,TVS等等!)否则容易出现EMS的问题!

更多技术设计应用及技术交流;请关注公众号

《电子产品:静电放电的分析与设计技巧》

《电子产品:EFT的设计与分析》

《电控板高级EMC设计与分析!》

更详细应用细节& EMC知识参考文献:

由于电子产品的EMC涉及的面比较广;我在课程中再对电子设计师遇到的实际问题,进行实战分析!先分析再设计;实现性价比最优化原则!