随着信号传输的高速化和高频化发展,对印制电路板的阻抗设计及控制精度要求日趋严格,以减少信号在传输过程中的反射、失真等,保持传输信号的完整性。PCB制作时由于图形分布均匀性、PP压合厚度均匀性、线宽均匀性及电镀均匀性等问题存在,会导致不同位置阻抗出现差异。本文通过在不同位置设计单端和差分阻抗线,综合分析图形分布、走线位置分布、铜厚等对阻抗一致性的影响,并对影响阻抗控制的关键因素进行分析,确定了影响阻抗一致性的主要因素及各因素作用强弱,可为PCB生产时提高PCB阻抗一致性提供参考和借鉴。

关键词:阻抗控制;阻抗一致性;介质层厚度;线宽;高速PCB

1 前言

近年来,随着电子技术的飞速发展,信号的上升沿时间越来越短,PCB信号传输频率和速度也不断提高[1]。同时,信号传输的高速化和高频化发展使得传输线效应日趋严重[2],信号在传输过程中更容易出现串扰、反射等问题,为保持传输信号的完整性、降低传输损耗,要求PCB在设计、制造过程中提高阻抗控制精度,尽可能地保证阻抗匹配[3]。对于高频、高速电路,PCB阻抗控制精度一般控制在10%或7%,部分产品要求控制在5%范围。

在生产过程中,PCB阻抗控制不仅要管控同一传输线的阻抗值在范围内(同一传输线阻抗波动性),还需要保证整板不同传输线均满足控制要求(不同传输线阻抗一致性)。由于图形内真实走线是弯曲的、多样的,无法对每组传输线进行测试。对于有阻抗控制要求的PCB,目前常见的做法是在PCB的拼版板边或板中间位置设计阻抗测试条,这些测试条与PCB有相同的叠层、线宽/线距等,可通过检测测试条的阻抗快速、方便地判断PCB的阻抗控制情况。但是,由于电镀边缘效应、层压板边溢胶大及线路蚀刻均匀性等因素的影响,测试条与真实走线的阻抗存在一定的差异,使得测试条的阻抗结果无法有效代表走线的真实阻抗值。同时,板内图形走线位置是多变的,有些传输线靠近拼版边缘,有些位于拼版的中间位置,而层压流胶、电镀和蚀刻均匀性等会影响拼版不同位置的阻抗值。为实现高精度阻抗控制,提高拼版内不同传输线的阻抗一致性,降低阻抗测试条与拼版内线路的阻抗差异,必须了解影响阻抗一致性的因素,并针对性地进行优化改进。

本文通过试验设计,针对拼版内阻抗一致性(真实走线之间、真实走线与阻抗测试条之间)的影响因素进行分析探讨,量化分析了拼版不同位置处的介质层厚度(简称介厚)、介电常数、线宽、铜厚及阻焊层均匀性对阻抗的影响,得出各因素对板边测试条与板内图形阻抗差异的影响大小,并对差异的形成原因进行具体分析,可为高速PCB阻抗精度及阻抗一致性控制提供参考。

2 试验方法

2.1 材料与设备

材料:规格为106、1080、3313的半固化片及0.1 mm芯板

设备:安捷伦E5071C网络分析仪,金相显微镜

2.2 试验原理及方法

2.2.1 不同位置阻抗差异及影响因素分析

采用不同含胶量的半固化片进行压合,并在同一板面距板边不同位置处设计50 Ω单端线和100 Ω差分线。制作完成后采用网络分析仪测试拼版不同位置阻抗,切片分析拼版不同位置介厚、线宽、铜厚差异。

流程设计:开料→内层图形→压合→钻孔→沉铜→板镀→外层图形→图形电镀→外层蚀刻→阻焊→沉金→测试

2.2.2 半固化片含胶量对不同位置介厚、介电常数及阻抗的影响分析

分别采用3张106、2张1080.和2张3313半固化片与1oz铜箔进行压合,而后蚀去铜箔并测量不同位置介厚差异,并通过软件模拟计算:(1)拼版不同位置因介质层厚度差导致的阻抗差异;(2)流胶差异对介质层介电常数的影响及由此导致的阻抗差异。

2.2.3 残铜率差异对介厚控制及电镀的影响

拼版内层图形采用线宽为177.8 μm的线路,通过调节线路间距获得残铜率分别为0%-100%的模块(步长为10%),外层残铜率设计为20%、33%和50%。蚀刻后切片分析拼版不同位置处介厚、线宽和铜厚差异,并采用软件计算其对阻抗的影响。

流程设计:开料→内层图形→压合→板镀→外层干膜→图形电镀→外层蚀刻→测试

3 结果与讨论

3.1 距板边不同距离处阻抗差异

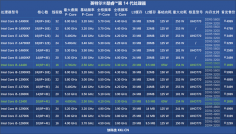

图6为拼版不同位置处单端线和差分线的阻抗测试结果及相应的介厚、线宽、铜厚变化曲线,由图6A和图6B可知,对于内层线路,靠近板边的单端线(距板边25 mm)的阻抗要比板中间小2~3 Ω,而板边差分线阻抗则比板中间小3~4 Ω,当线路距板边大于或等于50 mm时阻抗值变化幅度减小。对比图6A和图6B中的介厚、线宽、铜厚因素可知,三者中介厚受位置影响最大,且其变化规律与阻抗变化趋势几乎一致;不同位置处单端线宽和差分线宽差异在4 μm内,差异较小;而不同位置处铜厚变化则无特定规律,铜厚差异在1.5 μm内。因此,对于内层线路来说,影响不同位置阻抗一致性的最大因素是压合后的介厚均匀性,其次则是线宽。

由图6C和图6D可以看出,对于外层线路,与板边距离越大,阻抗值逐渐增大,当线路距板边大于75 mm时,阻抗值变化幅度较小,逐渐趋于稳定。对比不同位置处介厚、线宽、铜厚可知,板边(25 mm处)比板中间介厚小10 μm左右,线宽偏差在5 μm以内。由于电镀边缘效应,板边铜厚要比板中间大2.5 μm左右。因此,对于外层线路来说,影响不同位置阻抗一致性的最大因素也是介厚均匀性。

3.2 介厚均匀性及其对阻抗的影响

由前文可知,介厚均匀性对内层和外层阻抗一致性均有很大的影响,在阻抗设计时,介厚包括芯板的介质层厚度和半固化片压合后的厚度。一般来说,芯板的厚度均匀性较好,不同位置差异较小,但半固化片压合后的介厚及均匀性常与设计值存在偏差,实际生产板不同位置处介厚有所差异(尤其是板边和板中间区域),导致此差异的原因有:①图形分布不均(即残铜率不一致);②板边流胶速度较快,导致板边位置介厚偏薄。

(1)残铜率差异对介厚均匀性及阻抗的影响

对于不同型号PP,压合时流胶长度存在差异,当高残铜率区域、低残铜率或无铜区面积较大时,由于流胶长度限制,不同区域介厚必然存在差异,尤其是中心位置,由于周围胶的阻碍,高残铜率区域中心的胶难以填充至缺胶区域,而低残铜率区域中心也较难获得填胶。为此,我们通过理论模型计算出不同基铜厚度时由于残铜率差异导致的介厚差异,并计算其对阻抗的影响,其结果如表1所示。由表1可知,对于1 oz、0.5 oz和0.33 oz的铜厚,残铜率为80%和无铜区介厚差异分别为25.1 μm、12.2 μm、8.1 μm,以单端微带线为例,此介厚差异会导致阻抗相差4.65 Ω、2.36 Ω、1.59 Ω。

表1 残铜率差异导致的介质层厚度及阻抗差异

注: 阻抗计算采用单端微带线模型:Er=3.95,W=305 μm.

图4为单张2116压合后不同残铜率处实测介厚,由图可以看出,当铜厚为0.5 oz时,残铜率为0%与残铜率为100%区域介厚相差约为20 μm,也即残铜率每相差20%,会导致介厚相差约4 μm;当铜厚为1 oz时,0%与100%残铜率区域介厚相差约35.5 μm,也即残铜率每相差20%,会导致介厚相差约7.1 μm。图5为采用软件模拟计算的介厚差异导致的阻抗偏差,由图可知,对于外层单端线和外层差分线,介厚相差2.5 μm,阻抗偏差约0.6 Ω;对于内层单端线和差分线,介厚相差2.5 μm,阻抗偏差约为0.25 Ω和0.4 Ω。因此,板面不同位置处残铜率的差异会对阻抗造成很大的影响,尤其是铜厚较大时。在生产过程中,需尽量减少同一板面不同位置的残铜率差异,当残铜率差异较大时,在不影响电气性能的基础上合理铺设阻流点,减小拼版不同位置的介厚差异。

(2)含胶量对介厚均匀性及阻抗的影响

层压时,溢胶会导致板边介厚比板中间更薄,为研究板边不同距离处介厚差异,对不同规格PP压合后距板边不同距离处的介厚进行了分析,结果如图6所示。由图可知,同一规格PP,与板边距离越大,介厚呈增大趋势,当距板边75 mm时,介厚基本稳定;同时,PP含胶量越大,板边与板中间介厚差异越大(106 PP板边与板中间的介厚差约为0.19 mm,而3313 PP介厚差约为0.08 mm)。

为了更直观分析不同位置与板中间介厚差异,对图6的数据进行了处理,其结果如表2所示。由表可知,106与1080 PP压合后,板边25 mm处与板中间厚度偏差分别为10.53%和6.22%,而3313相对较低,偏差为4.81%,上述差异出现的原因是106与1080 PP的含胶量更高,压合时板边溢胶量相对较大,导致板边介厚偏小。