两个月前,也就是曾经的FPGA巨头Altera被英特尔收购的4年之后,英特尔推出了“全面借助自身能力”开发的新一代FPGA产品——Agilex。与此前Altera推出的Stratix、Arria、Cyclone、Max等产品系列完全不同,Agilex是一个全新的FPGA系列,“体现了你能想象到的所有与Intel相关的技术资源”,被英特尔寄予了更多的期待。

这里所提到的“相关技术资源”,基本上等同于英特尔在2018年底“架构日”上所提出的制程和封装、架构、内存和存储、互连、安全、软件这“六大技术支柱”。尽管当时英特尔官方表示将会尽快把六大技术支柱运用于自己的整个工程部门,落实在已经或即将推出的产品与技术规划中。但只用了不到半年的时间,Agilex FPGA就成为“六大技术支柱”落地的最佳载体,英特尔强大的系统研发和整合能力可见一斑。

窥一斑而知全豹

Agilex是Agile(敏捷)和Flexible(灵活)两个词语的结合体,而这两个特点也正是现代FPGA技术最为核心的两大要点。英特尔在2015年时就承诺说未来会根据不同的客户需求提供不同点5的异构架构,包括:分立的CPU+FPGA、封装集成的CPU+FPGA、以及将Intel CPU/FPGA/ARM三者进行管芯集成的FPGA。

理由是显而易见的。通过集成,不但能够降低延时,提高效能和性能/瓦,更可以统一处理器和FPGA之间的工具流程,为不同的性能需求提供更广泛的体系结构支持。4年之后,Agilex FPGA通过异构架构,实现了对不同制程工艺、不同逻辑单元之间的集成,在灵活性和定制化方面实现了突破。

根据英特尔2月份的基准测试,Agilex在最大时钟速率(Fmax)上比Stratix 10提高了40%,而总能耗降低高达40%。此外,Agilex还具有高达40 TFLOP的DSP性能(FP16配置)和92 TOP DSP性能(INT8配置)。

坦率的说,仅凭异构架构这一点,Agilex FPGA其实是无法实现上述性能指标的,那么,Agilex FPGA中还隐藏着哪些不为人知的“黑科技”呢?

10纳米工艺和高级3D封装

对于英特尔这样拥有“端到端”解决方案的半导体巨头来说,拥有先进的半导体制程技术和封装技术,是构建领先产品的基础与关键。在架构日以及随后的CES 2019展上,英特尔相继展示了覆盖云到端的10纳米产品,包括“Ice Lake”PC 处理器、“Lakefield”客户端平台、“Snow Ridge”网络系统芯片、“Ice Lake”英特尔至强可扩展处理器,以及被外界视为继2018年推出的嵌入式多芯片互连桥接(EMIB)封装技术之后,又一个具备“里程碑”意义的创新突破——“Foveros”3D封装技术。

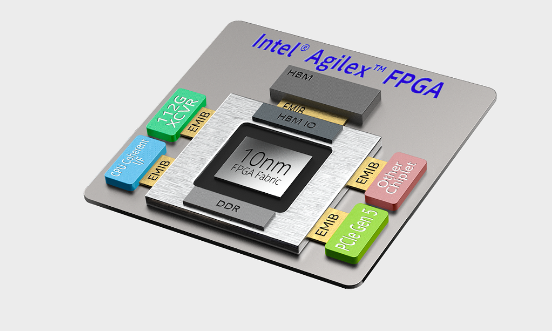

为了确保性能的一致性,Agilex FPGA器件核心的FPGA逻辑结构芯片同样采用了英特尔10纳米芯片制程技术构建,这也是目前世界上最先进的FinFET制程技术之一。同时,Agilex还融合了英特尔专有嵌入式多芯片互连桥接(EMIB)集成的 3D 异构系统级封装(SiP)技术,它提供了一种高性能、低成本的方法,有助于将Chiplets和FPGA逻辑结构芯片集成至相同的封装中。

第二代英特尔HyperFlex架构和Chiplets架构

Agilex FPGA的逻辑结构芯片采用了第二代英特尔HyperFlex架构,除了与第一代架构一样,在整个核心结构中都使用额外的寄存器Hyper-Registers外,二代架构还提升了整体结构性能,同时最大限度地降低了功耗,其中最显著的一项改进是在超级寄存器中添加了高速旁路。

而Chiplets是一种物理IP模块,可通过封装级集成方法和标准化接口集成其他Chiplets。借助Chiplets这种混合搭配模式,收发器数量不再受通道数量的限制。设计人员要想增加或减少收发器通道数量,只需添加所需的收发器Chiplets即可,无需重新布局芯片以集成不同数量的通道。仅此一项,英特尔就将单个收发器通道的速度从58Gbps提升到112Gbps。

高性能处理器接口

在数据中心里作为CPU的硬件加速器,用来加速深度学习的模型训练、金融计算、网络功能卸载等各类应用,是当前FPGA的一个主要应用场景。但该领域亟待解决的核心问题之一,就是缓存一致性。换句话说,就是必须要明确CPU与硬件加速器之间的内存互联协议。

今年3月,英特尔宣布联合微软、阿里、思科、戴尔EMC、Facebook、谷歌、惠普企业HPE和华为等公司,共同推出一个全新的互联标准,取名为Compute Express Link(CXL),应用目标锁定互联网数据中心、通信基础设施、云计算与云服务等领域,而这也正是FPGA大显身手的重要平台。

为了确保高性能在线处理和处理器负载加速,英特尔Agilex FPGA支持最新一代高性能处理器接口,包括PCIe Gen 5和CXL,并将成为首款采用Xeon可扩展处理器的一致的高速缓存和内存互联结构的FPGA。

先进的内存层级结构

Agilex FPGA 支持各个层级的内存资源,包括通过专用接口提供的嵌入式内存资源、封装内内存和片外内存。该层级结构的第一层是嵌入式片上内存,包括MLAB、块RAM和eSRAM,每种内存均可提供不同的容量,以满足不同的处理需求。此外,英特尔在设计中还使用SIP技术将高带宽内存(HBM)直接集成至Agilex FPGA器件中,有助于缩减电路板尺寸和成本,简化与降低电源需求。

另一个值得关注的重点是Agilex平台还集成了eASIC技术。这种集成eASIC芯片定制技术能够实现从FPGA到结构化ASIC的迁移。换句话说,用户可以利用eASIC自身具备的可复用 IP 的自定义逻辑连续体,在整个产品生命周期内进行灵活优化,快速从FPGA转移到ASIC。

软件

全新硬件架构每一个数量级的性能提升,软件能相应带来两个数量级的性能提升。在新一代Agilex FPGA上,配套支持软件Quartus Prime可缩短硬件开发者30%的编译时间,内存利用率也提高了15%。同时,新一代的Agilex FPGA也纳入到One API的架构当中。

即将于今年第四季度推出的“OneAPI”软件编程框架,,为软件开发者提供了单一源的异构编程环境,支持常见的性能库API、Intel VTune和Advisor等软件开发工具,能够将软件匹配到能最大程度加速软件代码的硬件上,用以简化包括FPGA、CPU、GPU、人工智能和其它加速器在内的各种计算引擎的编程接口,降低各种架构和工作负载下的开发复杂性,加速六大技术支柱的大规模部署。

迎接多元化计算时代

让我们先暂时跳出FPGA这个小圈子,来看看为什么英特尔要提出“六大技术支柱”?

有人说这“六大技术支柱”是英特尔为抵御NVIDIA、AMD和赛灵思等公司而筑起的坚固城防,也有人不惜溢美之词,将其称之为英特尔引领未来计算发展的“创新矩阵”。但其实无论叫法如何,在英特尔看来,这六大技术支柱之间是相互关联、紧密耦合的,既能够带来指数级的创新,也是英特尔未来十年甚至未来五十年的主要驱动力。

从英特尔发布的数据来看,其10nm工艺下的晶体管密度达到了100.8Mtr/mm2,大约是上一代的14nm工艺的2.7倍。也就是说在2015-2018这3年左右的时间内,英特尔实现了晶体管密度2.7倍的增长。同时,英特尔还正在积极研究如纳米线晶体管、III-V材料(如砷化镓和磷化铟)晶体管、硅晶片3D堆叠、高密度内存与互联、紫外光(EUV)光刻技术、自旋电子、神经元计算等前沿项目。

发展半导体精尖制造技术和平台,生产世界上最好的芯片,持续推动制程和封装工艺技术创新,当然是英特尔的使命,但还不是全部。

我们现在正逐渐转向以数据为中心的时代。预期到2020年,普通用户每天产生的数据量为1.5GB,智慧医院每天3TB,自动驾驶每天达4TB,而联网飞机和智慧工厂每天分别达到了40TB和1PB!

这意味着伴随着数据量的爆炸式增长,数据类型也发生革命性变化,人工智能、5G、自动驾驶、云计算、物联网等新兴应用带来了更加多元化的计算需求。例如在嵌入式应用领域和边缘设备端,用户的需求是能够实时抽取包括图像、视频和视觉信息在内的数据;在通信基础设施端,用户需要高带宽融合处理能力;在云端,相关企业的需求则是能够高效的管理、组织和处理激增的数据。

也就是说,当我们从更高的维度来看数据架构时,就会明显的意识到,在这个海量数据推动计算架构快速演进并呈指数级扩展的时代,没有一种单一的技术可以全面满足消费者或企业客户对未来的计算需求,不可能只通过直接的标量架构就能解决所有应用,他们需要的是在多样化的层级结构中连接多样化的架构,比如分别应用于CPU、GPU、AI和FPGA产品中的标量(Scalar)、矢量(Vector)、矩阵(Matrix)和空间(Spatial)架构。

同时,随着从高度动态、非结构化自然数据中进行收集、分析和决策的需求越来越高,对计算的需求也超越了经典的CPU和GPU架构。虽然领先的制程和CPU仍然至关重要,但要想充分把握数据爆发带来的机遇,还需要在包括制程和封装、架构、内存和存储、互连、安全、软件在内的一系列基础构建模块上极速创新。那种不去研究数据的产生、类别、以及所需要的处理能力,是不行的。这和以前的通用数据处理不一样,只单纯强调某一种处理器算力的做法是行不通的。

英特尔希望能通过六大技术支柱引领“超异构计算”时代。即通过提供多样化的标量、矢量、矩阵和空间计算架构组合,以先进制程技术进行设计,由颠覆性内存层次结构提供支持,通过先进封装集成到系统中,使用光速互连进行超大规模部署,提供统一的软件开发接口以及安全功能。

以英特尔在CES 2019上展示的下一代CPU微架构Sunny Cove为例,它包含了可加速人工智能和加密等专用计算任务的新功能,旨在提高通用计算任务下每时钟计算性能和降低功耗。在即将量产的10纳米PC处理器Ice Lake中,就高度整合了Sunny Cove微架构、AI使用加速指令集以及英特尔第11代核心显卡。

为什么要把制程封装和架构设计组合在一起?因为通过超异构计算,英特尔可以集成不同架构、不同制程、3D封装、互连和OneAPI等技术,确保可以最有效地实现产品多样性,提升产品稳定度,快速满足客户定制化和市场化的需求。

在向数据公司转型的过程中,英特尔将自身定义为端到端方案提供商,即产品线覆盖云端、网络传输端和终端。其中,核心来自云端的大规模数据处理,而布局端到端则可以让英特尔掌握“数据什么时候来、是什么样的数据、需要怎么来处理”。

为了增进处理新数据的能力,加快技术发展的步伐,并推动PC和服务器以外的计算,英特尔过去六年来不但一直在研究能够加快经典计算平台的专用架构,还同时加大了对人工智能(AI)和神经拟态计算的投资和研发。完成了制造和封装的首款自主学习神经拟态测试芯片Loihi、已交付的49量子位超导量子测试芯片、在300毫米晶圆制程上发明的自旋量子位制造流程等,均被业界视作英特尔对未来计算的提前布局,旨在颠覆未来计算格局。

随着人工智能、物联网、传感器等技术的融合应用及进一步发展,越来越多无人干预的机器设备和应用场景成为可能,“自能(Autonomous)”也正取代“智能”,成为带动新一轮创新发展的新趋势。在这样的时代大背景下,英特尔战略性地跳出了单纯比拼工艺和算力的低层次竞争格局,站在更高的起点上,通过构建全新的六大技术创新组合,将CPU、GPU、FPGA、AI加速器、通信系统、高速存储等部分有机的结合到一起,重新定义了产品开发设计的模式,Agilex FPGA就是最佳印证之一。我们也期待看到更多基于六大技术支柱打造的产品上市,引领产业更好地解决多元化计算需求的挑战。