十二、芯片

35. 技术:流程

硅片切好之后,就要在晶圆上把成千上万的电路装起来的,干这活的就叫“晶圆厂”。各位拍脑袋想想,以目前人类的技术,怎样才能完成这种操作?

用原子操纵术?想多了,朋友!等你练成御剑飞行的时候,人类还不见得能操纵一个一个原子组成各种器件,那究竟怎么做呢?

在开始前,我们要先认识 IC 芯片是什么。IC 全名积体电路(Integrated Circuit),由它的命名可知它是将设计好的电路,以堆叠的方式组合起来。藉由这个方法,我们可以减少连接电路时所需耗费的面积。下图为 IC 电路的 3D 图,从图中可以看出它的结构就像房子的樑和柱,一层一层堆叠,这也就是为何会将 IC 制造比拟成盖房子

从上图中 IC 芯片的 3D 剖面图来看,底部深蓝色的部分就是上一篇介绍的晶圆,从这张图可以更明确的知道,晶圆基板在芯片中扮演的角色是何等重要。至于红色以及土黄色的部分,则是于 IC 制作时要完成的地方。

首先,在这里可以将红色的部分比拟成高楼中的一楼大厅。一楼大厅,是一栋房子的门户,出入都由这里,在掌握交通下通常会有较多的机能性。因此,和其他楼层相比,在兴建时会比较复杂,需要较多的步骤。在 IC 电路中,这个大厅就是逻辑闸层,它是整颗 IC 中最重要的部分,藉由将多种逻辑闸组合在一起,完成功能齐全的 IC 芯片。

黄色的部分,则像是一般的楼层。和一楼相比,不会有太复杂的构造,而且每层楼在兴建时也不会有太多变化。这一层的目的,是将红色部分的逻辑闸相连在一起。之所以需要这么多层,是因为有太多线路要连结在一起,在单层无法容纳所有的线路下,就要多叠几层来达成这个目标了。在这之中,不同层的线路会上下相连以满足接线的需求。

分层施工,逐层架构

知道 IC 的构造后,接下来要介绍该如何制作。试想一下,如果要以油漆喷罐做精细作图时,我们需先割出图形的遮盖板,盖在纸上。接着再将油漆均匀地喷在纸上,待油漆乾后,再将遮板拿开。不断的重复这个步骤后,便可完成整齐且复杂的图形。制造 IC 就是以类似的方式,藉由遮盖的方式一层一层的堆叠起来,详细工艺下面详细介绍

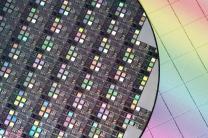

最后便会在一整片晶圆上完成很多 IC 芯片,接下来只要将完成的方形 IC 芯片剪下,便可送到封测厂做封装测试,至于封测厂是什么东西?请持续关注本公众号史晨星(shichenxing1)

36. 技术:工艺

集成电路制造工艺繁多复杂,晶圆厂厂内大致上可分为四大区:真空区、黄光区、蚀刻区、扩散区

真空区:乃沉积暨离子植入,也就是在晶圆上覆盖一层薄膜,所以也称为薄膜区。薄膜沉积工艺系在晶圆上沉积一层待处理的薄膜,薄膜工艺常用于在晶圆表面制备各类半导体、绝缘体、金属的薄膜材料,包含CVD、PVD(蒸发和溅射)、电镀、外延等;沉积工艺包括化学沉积和物理沉积,形成多层的光刻和刻蚀立体结构,构成绝缘层或金属导电层,详细请持续关注本公众号史晨星(shichenxing1)设备篇

黄光区:主要是使电路图显影,匀胶工艺系把光刻胶涂抹在薄膜上,光刻和显影工艺系把光罩上的图形转移到光刻胶,集成电路的最小线宽取决于光刻设备的分辨率,它定义了半导体器件尺寸,光刻的工艺水平直接决定芯片的制程水平和性能水平,详细请持续关注本公众号史晨星(shichenxing1)设备篇

蚀刻区:使用化学剂来蚀刻出所需要的电路,刻蚀工艺系把光刻胶上图形转移到薄膜,去除光刻胶后,即完成图形从光罩到晶圆的转移,将没有受光阻保护的硅晶圆,以离子束蚀刻,刻蚀工艺的提高在于不断缩小PN间的闸极,详细请持续关注本公众号史晨星(shichenxing1)设备篇

扩散区:又称为炉管区均为高温加工的处理,掺杂工艺是形成N型和P型掺杂结构的过程,包含扩散和离子注入两类;离子注入工艺对硅基材料进行掺杂,形成PN区,构成晶体管,详细请持续关注本公众号史晨星(shichenxing1)设备篇

上述四大工艺循环,分层施工,逐层架构,最终完成芯片制作

37. 技术路线:制程

半导体产业技术进步主要有两大方向:一是硅片直径越大→硅片面积越大→单个晶圆上芯片数量越多→效率越高→成本越低,详细请参考上篇文章半导体全面分析(三):制造三大工艺,硅片五大巨头!,二是制程越小→晶体管越小→相同面积上的元件数越多→性能越高→产品越好,那么制程是什么呢,下面详细介绍