图2:DDR5与DDR4相比的性能优势(资料来源:Micron)

除了在核心性能上的突破,DDR5还在可靠性、可用性与服务性 (RAS)上,以及可操作性上做了诸多优化。

芯片内建错误校正码 (ECC):通过DDR5器件输出数据之前在READ命令期间执行校正,减轻系统错误校正的负担。在DDR4内存上实现ECC功能,需要额外增加一颗芯片,而DDR5原生支持片上ECC,对于提升系统可靠性大有帮助。

PPR强化功能:包括hPPR (硬) 和sPPR (软)两个独立的修复功能。主要的优化在于减少了执行sPPR修复之前需要Bank中备份的列,这样可以将备份和储存大量信息所需的系统时间缩至最短,通常每列数据约2μs。

多用途命令 (MPC):DDR5时钟频率的提高,也给初始化和训练之前的操作执行带来挑战。为此,DDR5使用多用途命令 (MPC) 来执行介面初始化、训练和定期校正等功能,提升操作的效率。

从上文可以看出,一方面DDR5通过增加Bank组、增加突发长度、引入新的REFsb刷新命令等举措,提升核心性能,降低用户总体拥有成本;另一方面通过优化RAS和可操作性为开发和应用带来更大便利,这样双管齐下,为DDR5标准打造了稳固的根基。

表1:DDR5产品特色与功能优化(资料来源:安富利)

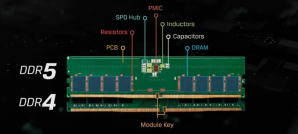

DDR5内存条的变化

当然,想要最大程度上释放出一个全新内存标准的威力,DIMM内存模块的设计也十分重要。DDR5标准的顺利升级,也必然需要内存模块方案的变化,为其提供助力。从Micron提供的技术文档中我们可以看到,这样的变化主要体现在以下几个方面:

首先,DDR5模块与DDR4模块最大的差别就在于,标准的DDR5模块中有两个独立的子通道,每个子通道最多有两个实体封装的存储器区块 (rank)。每个DRAM封装都可设为主要/辅助拓扑,进而增加逻辑存储器区块以提高密度。独立子通道能提高并行性,并支持存储器控制器更有效率地安排时序,进而打破数据传输量的限制,满足服务器等应用中日益增加的运算需求。

其次,DDR5中增加了本地的PMIC进行电压调节,由于将电源管理的功能从主板转到更靠近内存芯片的模块上,因此这种电源架构可降低主板的复杂性、提升电源转换的效率、增加更多电源管理的功能。

再有,DDR5模块上引入了基于MIPI I3C通讯协定的边带存取功能,能够更好地支持模块上越来越多的主动器件,提高可用性,并监控关键参数以掌握模块工作时与功率、散热等相关的详细信息。

此外,在L/RDIMM模块上,还放置了一对温度传感器IC,对模块表面温度梯度变化进行持续监测,并以此为依据调整流量变化,或者改变风扇速度,通过调优来最大化系统的处理能力。

最后,DDR5模块设计的改变,也催生了CAI、MIR和扩展接地等其他新功能,以利于改善设计配置、电源噪声和模块信号隔离等特性。命令和地址上的ODT及增强的 DQ/DQS/CA/CS 训练等新功能,也可提供更好的信号处理能效、更快的时钟速率,最终实现更高的带宽。

表2:DDR5与DDR4性能比较与优化(资料来源:安富利)

用DDR5开始一个新设计

可以想见,在即将到来的2021年,如何将计算存储方案升级到DDR5,将成为很多开发者——特别是数据中心等计算密集型应用的开发者——案头上的一个重要课题。为了加速这个进程,DDR5的核心技术供应商在快马加鞭推出新产品之外,也纷纷推出了开发者支持计划,比如Micron的DDR5 技术支持计划 (TEP)中,就为经过核准通过的合伙伙伴提供了丰富的技术资源,如:

1.产品数据手册、电气模型、热模型和仿真模型等技术资源,以帮助其产品开发和平台搭建

2.选择可用的DDR5元件与模块样品

3.与其他生态系统合作伙伴建立联系,以助其进行DDR5可用平台的设计与搭建

4.技术支持和培训资料

简言之,在需求发展的大趋势下,面对DDR5,除了“升级”跟上技术进步的节奏,实际上我们没有其他的选择。现在的关键就在于,如何在升级的这条路上走得更快、更顺畅。为此,安富利作为全球领先的技术分销商,也会为你提供全面和专业的支持。