文︱MARK LAPEDUS

来源︱Semiconductor Engineering

编译 | 编辑部

随着各种各样新的封装类型逐渐成为主流,先进封装互连技术正面临发展的转折点。一些供应商选择扩展传统凸块封装方法,而另一些则推出新的封装技术取而代之。

在任何情况下,目标都是在需处理的数据量增加时确保IC封装组件之间的信号完整性。但随着设备不断缩小,而越来越多的组件被添加到先进封装中来处理、移动和存储更多数据,将需要具有更多I/O的新技术。因此,尽管在可预见的未来中仍将使用传统的焊球和/或铜微凸块,但那些增强或取代传统互连技术、增加I/O数量并提供更多微缩空间的新技术正在研发中。

一如既往,尺寸和成本是决定性因素。铜微凸块比焊球/凸块更小,可在封装中实现更多 I/O。当前,先进封装技术的微凸块间距最小达40μm,这相当于20μm至25μm的凸块尺寸,裸晶上相邻凸块之间的间距为15μm。

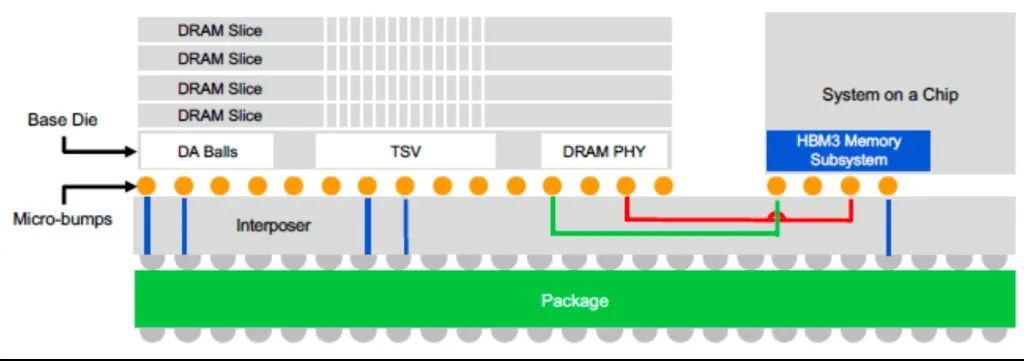

图 1:具有HBM3内存的2.5D/3D系统架构。铜微凸块连接中介层和基片。微凸块也用于芯片到芯片的连接。图源:Rambus

对于小于40μm的间距,客户在封装上有另外一些选择。首先,他们可以使用现有的凸块技术研发新的封装技术,以突破技术瓶颈,将当前40μm间距向下微缩至10μm。另一种选择是被称为铜混合键合的新技术。在混合键合技术中,裸晶的连接并非通过封装中的凸块。相反,该技术利用微小的铜对铜互连,实现比传统封装具有更多I/O的更窄间距封装。对于封装技术来说,混合键合的间距至少在10μm及以下。

AMD已经计划在未来的处理器产品中采用混合键合技术。该公司正在使用台积电的混合键合技术。其他代工厂也在研究混合键合。但并非所有封装都需要混合键合,且该技术针对的是高端产品。即便如此,混合键合仍然是一个昂贵且困难的工艺。

英特尔和其他公司并没有转向混合键合,而是希望扩展现有的凸点互连技术,并围绕这些技术开发间距小于40μm的封装。“在保持与现有硅和封装技术兼容的同时,利用现有的基础设施,将焊料微凸点互连微缩至更小的间距可能仍然是有利的,”英特尔封装开发工程师Zhaozhi Li在最近的ECTC大会上表示。

英特尔描述了一种将凸点间距缩小或减小到10μm的方法。一些OSAT也在研究更窄间距的铜凸点技术。但是,随着焊料/铜凸点技术逐渐向更窄间距微缩,面临的挑战也随之增多。对于新材料、新工艺和新工具的需求越来越多。尽管如此,下一代凸块技术和混合键合都将在该行业中发挥重要作用,推动着技术朝着更多先进封装和Chiplet模型发展。对于Chiplet,芯片制造商可能在库中拥有模块化裸晶菜单。然后,客户可以将芯片混合搭配并集成到现有封装类型或新架构中。

Chiplet正在成为推进芯片设计的替代方案。传统上,为了推进设计,供应商会开发片上系统 (SoC) 并在每一代设备上集成更多功能。但随着摩尔定律延缓,芯片集成变得越来越困难和昂贵。虽然这种方法仍然是新设计的一种选择,但Chiplet有望成为下一代芯片设计趋势。混合键合或缩放凸块是Chiplet拼图中的关键部分。

封装技术概述

IC封装将裸晶包裹在封闭式单元中,可保护器件免受损坏。封装还可以提高裸晶的性能。

“业界正在加大对先进封装的投资,并致力于提高系统级互连密度、降低功耗、实现更小的外形尺寸,并通过缩小封装级间距,以及将更多功能集成到单个封装中来降低成本。” Brewer Science的高级项目经理Xiao Liu表示。该行业已开发出超过1000种不同的封装技术。客户可根据给定的应用程序进行选择。

按照互连类型来细分封装市场,包括引线键合、倒装芯片、晶圆级封装 (WLP) 和硅通孔 (TSV)。TSV提供最多的I/O,其次是WLP、倒装芯片和引线键合。

据TechSearch称,大约75%到80%的封装基于引线键合。焊线机使用细线将一个芯片缝合到另一个芯片或基板上。引线键合机用于制造商品和中档封装以及内存堆栈。

倒装芯片在芯片顶部形成微小的焊料或铜凸点。然后将器件翻转并安装在单独的裸晶或板上。凸块落在铜焊盘上,形成电气连接。

在此过程中,使用高速倒装芯片键合机连接凸块裸晶,然后进行大规模回流工艺。“许多倒装芯片设备不需要窄间距。它们可以通过大规模回流来完成,”Kulicke & Soffa (K&S) 的CTO Bob Chylak表示。“倒装芯片键合机取出芯片,将焊球浸入助焊剂中,然后将它们放置在PCB 上。然后PCB通过回流烘箱,回流烘箱将焊料熔化,然后将其固化。”

倒装芯片用于开发许多封装类型,例如球栅阵列(BGA)。图形芯片和处理器采用BGA封装。在倒装芯片中,芯片上的凸点间距范围从300μm到50μm。

“我们仍然看到140μm至150μm的宽间距封装。该技术仍然是发展主流,并且不会很快改变,”QP Technologies的母公司Promex CTO Annette Teng认为。“我们开始看到一些 110μm到120μm的封装技术。40μm以下仍处于研发阶段。”

同时,扇出封装是一种晶圆级封装。在扇出封装的一个示例中,DRAM裸晶堆叠在逻辑芯片上。

TSV用于先进2.5D/3D封装,通常用于高端系统。在 2.5D/3D封装中,裸晶堆叠或并排放置在中介层的顶部,中介层包含TSV。TSV提供了从裸晶到电路板的电气连接。在2.5D的一个示例中,ASIC和高带宽存储器(HBM)并排放置在中介层上。(HBM是DRAM内存堆栈。)

2.5D封装的焊球位于基板底部,将封装与电路板进行电气连接。C4凸点是较小的结构,将基板连接到中介层。较小的铜微凸块将中介层连接到基片上。在HBM中,DRAM裸晶使用 40μm间距的微小微凸块连接。

为了堆叠和连接这些封装中的裸晶,热压键合机(TCB)系统拾取裸晶并将凸块与另一个裸晶的凸块对齐。该系统使用压力和热能来键合凸块。

展望未来,供应商希望开发凸点间距低于40μm的HBM模块和3D封装,从而实现更多的 I/O和带宽。芯片客户可以通过使用更精细的凸点或使用铜混合键合来开发先进封装。有些客户则可能对不同封装同时使用这两种方法。

预计铜凸点的间距将从40μm微缩至10μm。然后,封装技术逐渐走向混合键合,从而实现 10μm及以下间距的互连。但并非所有封装厂都可以开发混合键合。对于大多数OSAT来说,这项技术成本过高,需要昂贵的半导体晶圆厂来实现这些工艺。

精选代工厂是供应商仅有的能够将混合键合投入生产的方法。即便如此,用于封装的混合键合仍然具有挑战性。“混合键合面临的巨大挑战是晶圆表面清洁度、晶圆翘曲以及芯片中铜和介电材料之间的梯度,”UMC技术总监Tony Lin表示。

混合键合仍面临很多问题。“未来几年肯定会推出具有非常窄间距(使用混合键合)的产品。” Amkor高级封装开发和集成副总裁Mike Kelly表示。“这是一个昂贵的工艺,并且未来几年可能仍将是超高性能的领军者。”

凸块微缩

考虑到这一点,英特尔和其他公司正在使用低于40μm的传统微凸块开发新的先进封装技术。供应商还在研究下一代HBM技术HBM3,其凸点密度是HBM2e的两倍。HBM3支持 8.4Gbps的带宽,而HBM2e的带宽为3.6Gbps。

微缩微凸点具有以下几点优势。首先,它利用了现有的焊料/铜凸点基础设施。其次,几家供应商正在研究窄间距凸点技术,例如Amkor、ASE、Intel、JCET、三星和台积电。

开发带有凸块的封装技术并非新鲜事。在1960年,倒装芯片封装作为一种组装技术出现。最初,倒装芯片工艺涉及到C4(受控塌陷芯片连接)凸点的形成,其直径范围为75μm至200μm。

C4凸块仍在封装中使用,但它们是宽间距结构。因此,从2006年的65nm节点开始,英特尔和其他公司逐渐迁移到更小的C4凸点版本,称为铜微凸点/柱,有时也称为C2凸点。最初的铜微凸点直径为25μm。

铜凸点由带有薄镍扩散阻挡层的铜柱和锡银焊帽组成。“C2凸点提供比C4凸点更好的热性能和电气性能。这是因为Cu的热导率和电阻率优于焊料,” Unimicron CTO John Lau在他的新书《半导体先进封装》(Springer,2021年)中表示。

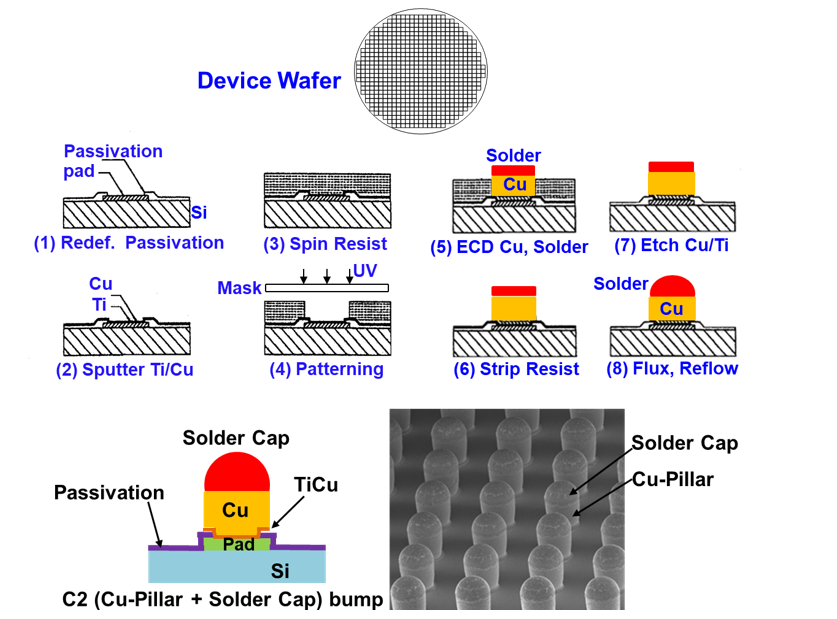

为了制造更小的铜微凸块,该工艺类似于C4流程。首先,芯片在晶圆厂的晶圆上加工。然后在晶片底部形成凸块。

为此,使用沉积法通过凸点下金属化层(UBM) 沉积表面。然后,在UBM上应用一种称为光刻胶的光敏材料。使用光刻系统在抗蚀剂顶部图案化预定凸块尺寸。该图案被蚀刻,形成一个小间隙。

使用电化学沉积(ECD)系统,填充间隙或将间隙镀铜。剥离抗蚀剂并蚀刻结构。该结构在烘箱中回流或加热,形成凸块。

图 2:微凸点工艺流程。图源:John Lau,Unimicron

当今最先进的微凸块使用40μm间距和20μm至25μm之间的凸块尺寸。据DuPont称,凸块尺寸约为凸块间距的50%。

未来的封装将转向具有更窄间距的更小铜凸点。“我们看到柱状凸块尺寸已经有18μm间距、9μm直径和20μm高。300毫米晶圆上有大约2亿个凸点,间距为18微米。”Onto Innovation产品营销经理Woo Young Han表示。“我们听说一位客户声称实现10μm间距、5μm直径和10μm高。在10μm间距的300mm晶圆上大约有5亿个凸点。5μm的凸点直径是我们从客户那里听到的最小的直径。”

向更小的凸块研究会带来一些挑战。“随着焊料凸点间距的缩小,凸点高度变短,可用于键合的凸点表面减少,芯片级凸点数量增加,”Han表示。“随着凸点数量的增加,凸点尺寸的减少转化为更小的错误余量,以建立可靠的电气连接。随着凸块间距的缩小,芯片级凸块共面性、凸块表面粗糙度和凸块硬度变得越来越重要。键合过程中使用的温度、时间和压力取决于芯片级凸块共面性、凸块表面粗糙度和凸块硬度的质量。在键合过程中使用更高的温度、更长的时间和更大的压力会增加成本和损坏芯片的风险。”

所有这些都在整个制造流程中提出了几个挑战。以蚀刻为例。“铜柱和焊料凸点的直径更小。由于蚀刻导致的下切变得越来越重要,” Unimicron的Lau表示。

ECD电镀工艺也面临挑战。“随着客户瞄准下一代微凸点解决方案,电镀均匀性和共面性控制变得越来越重要,”Lam Research董事总经理Manish Ranjan表示。“Lam的电镀槽设计可提供超高均匀对流,以实现快速且均匀的沉积速率。此外,专有技术解决方案,例如先进的表面处理能力,可实现最低的缺陷性能。”

最重要的是,向更小凸块的转变也可能需要全新且差异性的凸块结构。考虑一个间距为40μm、凸块高度为25μm 的微凸块。在这个凸块中,铜结构的高度是15μm,而镍是5μm。剩下的部分是焊帽。

“在这种结构中,铜比镍大,”DuPont先进封装技术全球营销负责人Shashi Gupta表示。“当你采用更窄的间距时,铜的高度将开始缩小。在某些时候,铜的厚度和镍的厚度或多或少相差不大。焊帽也在缩小。”

在一个假设示例中,未来的铜柱可能具有3μm的铜结构、3μm的镍阻挡层和5μm的焊帽。“关键是镍和铜非常相似。在这种厚度下,要在整个晶圆上保持均匀性是一项挑战,”Gupta表示。“因此,您可能需要考虑在焊料在顶部的柱状结构中选择一种金属。”

换句话说,在更窄间距的封装中,您可能有一个带有焊帽的微小铜柱,或带有焊帽的镍柱。“出于成本、产量或性能方面的考虑,通常使用铜/锡-银或镍/锡-银结构而不是铜/镍/锡-银结构,”Gupta称。“这将有助于优化成本结构,也更容易控制质量。”

与镍相比,铜是一种更佳的金属,但铜也有一些缺点。镍的导电性较低,但镍凸点也可能起作用。这仍处于研发阶段,尚不清楚镍在生产中如何应用。

尽管如此,在未来的工艺中,铜凸块将只需要镀铜工艺,而镍凸块将使用镀镍工艺。

这反过来又简化了电镀过程。“与镀两层(先镀铜,再镀镍)相比,镀单层铜或镍更容易。然后将相同的焊料以减少的体积量放在其上,”Gupta说。

最终,两种不同的凸块金属结合在一起,并扩散到彼此的晶界中。这称为金属间化合物 (IMC) 层。在某些情况下,IMC 很稳固。另一些情况下,IMC较脆弱,导致连接失效。

IMC是可能出现问题的地方。“对于铜/锡-银凸点结构,焊料直接沉积在铜柱上而没有镍阻挡层,在回流期间可能会形成金属间化合物 (IMC) 层,”Gupta表示。“IMC层可能会在老化或加热过程中继续生长,从而对焊点可靠性和导电性产生负面影响。相比之下,均匀镀镍代替铜柱可有效限制广泛的 IMC生长,并提供出色的阻挡能力、可焊性和其他特性,这些特性对于一致的晶圆制造至关重要。从工艺角度来看,更新的镍基电镀选项也是可持续的。”

图 3:通用支柱设计和先进微支柱设计。图源:DuPont

凸点键合

制造微小的凸块极具挑战性。在更窄的间距下将它们键合起来也很困难。

通过大规模回流的传统倒装芯片键合在更窄的间距上面临挑战。“标准回流工艺是在用于倒装芯片和系统级封装的烘箱中进行的。该解决方案以数量与低价著称,”JCET现场应用工程高级总监Nokibul Islam表示。“令人担忧的是,可能会出现基板和芯片之间的整体热膨胀系数不匹配,从而导致更高的翘曲和芯片移位。”

传统的倒装芯片工艺可以应用到50μm或40μm的间距,但再往下走就可能会出现可靠性问题。这就是TCB适用的地方。早在几年前,TCB已经推出,用于先进的窄间距键合应用。一些供应商在销售TCB工具。

TCB工具用于键合具有间距在40μm至50μm及以下微小凸块的裸晶,适用于芯片到晶圆和芯片到基板的应用。就目前情况而言,TCB微缩至10μm间距。

“热压键合是局部回流,”K&S的Chylak表示。“热压焊机不是加热整个电路板及其上的所有芯片,而是像普通倒装芯片一样抓住芯片,并将其浸入助焊剂中,然后将其放置在PCB上。键合机顶部有一个加热器。加热至超过将芯片固定到位的焊料熔点。然后冷却下来,使焊料凝固。”

助焊剂是用来去除试图键合的铜垫上的氧化物。在化学反应中,助焊剂将会溶解氧化物。

然而,TCB是一个相对缓慢的过程,存在一些助焊剂清洁问题。“倒装芯片和热压键合都存在问题。浸入凸块的助焊剂必须是清洁的。”Chylak表示。

业界使用清洁系统来清除封装中的助焊剂。这适用于宽间距应用,但此过程需要时间来清洁窄间距封装的助焊剂。

在另一个可能的解决方案中,业界开发了“免清洗助焊剂”材料。这些材料并不总是有效。如果过程中出现助焊剂,则很难清洁。

因此,K&S正在开发无助焊剂TCB技术。在TCB工具中,K&S 结合了原位甲酸蒸汽输送系统和腔室。“我们可以放一层甲酸蒸汽,它可以在没有助焊剂的情况下清洁表面,然后我们进行键合。这是我们开发的一项新技术,无需助焊剂即可键合。这是对TCB的生产力和可靠性的改进,” Chylak表示。

还有其他解决方案。在ECTC上,作为ASE的一部分,Siliconware描述了一种开发具有20μm 凸点间距的3D封装的方法,旨在堆叠和键合两个薄芯片。共有两种测试方案。一种使用带有毛细管底部填充 (TCCUF) 的TCB。另一个使用带有非导电膏 (TCNCP) 的TCB。

“总而言之,我们已经成功地表征和开发了使用20?m凸点间距的3D封装技术。这种封装技术可以通过标准的裸晶贴装和回流,以及使用NCF的热压焊来实现,”Siliconware的技术经理Mu Hsuan Chan表示。

与此同时,英特尔找到了一种方法来微缩20μm和10μm间距的微凸块。英特尔开发了带有微小凸块的裸晶,并通过对准精度优于2.1μm 的TCB工具将它们键合起来。

“数据表明,使用功能强大的TCB工具和紧密的键合工艺控制,将Cu/SnAg微凸块配置在20μm 间距下是可行的。然而,在10μm处,为了保留焊料以满足TCB键合的需要,并获得足够的键合工艺余量,需要放置一定的焊料/Cu扩散阻挡金属。”英特尔的 Li 说。

总结

最终,英特尔和其他公司将采用混合键合技术。台积电希望在这项技术上早日取得突破性进展。

但无论是窄间距封装还是宽间距封装,未来一段时间内,凸块封装技术仍将持续发展。尽管如此,先进凸块和混合键合都将为新的先进封装技术提供窄间距互连。不止一种封装技术选择对企业来说非常利好。