一则“辟谣”声明,让芯片堆叠、Chiplet再次成为市场上的焦点。

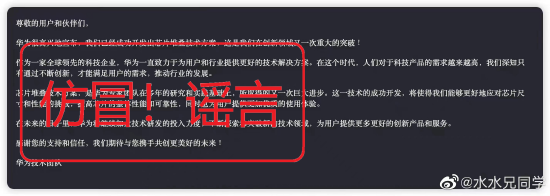

3月14日,市场上开始流传一则传闻,华为已经成功研发出芯片堆叠技术。上述传闻,很大程度上刺激了带动了A股芯片板块的上涨,与华为关系密切的中芯国际更是大涨超10%。

当日晚间华为正式辟谣,第二天半导体板块热度出现明显下降,截至3月15日收盘,中芯国际和其所在的半导体板块涨幅仅分别为1.81%和0.06%。

传闻背后,芯片堆叠、Chiplet等技术背后的进展,也引起行业人士的关注。多总管研究发现,国内Chiplet业务真正实现量产的企业较少,与国际巨头仍有明显差距,相关技术的崛起仍然任重道远。

都是制程惹的祸?

芯片堆叠和此前市场上大火的Chiplet同属3D封装技术,即通过将几块芯片整合成一块,最终在制程工艺不变的情况下,达到性能提升的目标。

其中,芯片堆叠技术,是指将多颗芯片“堆叠”在一起,以实现更高的集成度和更强的性能。根据网上传言的描述,华为的芯片堆叠技术,可将两块14nm的芯片能实现堆叠,在性能方面达到7nm芯片的水准。

而包括芯片堆叠、Chiplet在内的技术方案的出现,背后反映的是当前市场对解决先进制程受限的迫切渴望。

科技的迅猛发展,对芯片算力的要求不断提升,不少主流芯片厂商开始追逐更先进的制程工艺。然而,伴随摩尔定律逼近物理极限,提升制程工艺、芯片面积,将面临大幅的良率下降、成本增加、性能提升收益边际降低等问题。

目前,芯片制程工艺被认为已接近极限,台积电等厂商已将制程推进到3nm,未来再次升级迭代需要付出极大的成本。

另一方面,美国对中国半导体产业持续打压,限制中国获取先进制程芯片产品和代工服务,对于国内 AI 芯片厂商而言,通过芯片堆叠、Chiplet等架构创新的方式,或将成为提升算力另辟蹊径的选择。

Chiplet或开启千亿市场

和芯片堆叠技术相比,Chiplet技术目前在国内外已经取得了一定的进展。

Chiplet也称“小芯片”或“芯粒”,是将一个功能丰富、面积较大的芯片裸片(die)拆分成多个芯粒(chiplet),将上述芯粒组合在一起,通过先进封装的形式(如3D封装),集成封装在一起即可组成一个系统芯片。

研究人士认为,Chiplet技术可以突破先进制程的封锁,并大幅提升大型芯片的良率,降低设计的复杂程度和设计成本,同时还可降低芯片制造成本。

Chiplet发展或涉及整个半导体产业链,影响从EDA厂商、晶圆制造和封装公司、芯粒IP供应商、Chiplet产品及系统设计公司到Fabless设计厂商的产业链各个环节的参与者。

值得注意的是,Chiplet技术是当先进制程遇到瓶颈,同时面临良率低、价格高问题时的一种具有性价比优势的、可选择的技术路线,而仅仅通过先进封装技术,来弥补前道工序的不足,是远远不够的。

同样的情况也存在于芯片堆叠技术中,芯片堆叠并不能实现“1+1>2”的效果,最多只将芯片性能在原基础上略有提升,无法达到媲美先进工艺制程实力。

因此,Chiplet技术能缩短国内技术和西方大厂的技术差距,起到“弯道加速”的作用,但并不是先进芯片制造的替代品,中国半导体在大力拓展先进封装技术的同时,也需要在先进制造方面努力发展,双管齐下才能真正实现大的跨越。

Chiplet技术从出现以来,就受到市场的广泛关注。英特尔公司高级副总裁、中国区董事长王锐在2022世界集成电路大会上表示,Chiplet技术是产业链生产效率进一步优化的必然选择。

有机构预测,Chiplet技术可应用在自动驾驶、数据中心、消费电子、高性能计算、高端智能芯片等领域,2024年Chiplet市场规模将达58亿美元,2035年则将超过570亿美元。

17家“概念股”仅3家“量产”

近来,Chiplet概念成为二级市场最热门的题材之一,相关概念股持续拉升。不过,与其在二级市场上的火热相比,Chiplet业务在国内的推进则稍显滞后。

东方财富上“Chiplet概念”板块包括17家A股上市公司,多总管统计到,明确表示相关业务实现量产的上市公司仅有3家,分别是通富微电、华天科技和长电科技。

通富微电是国内规模最大、产品品种最多的集成电路封装测试企业之一。公司在互动易等平台表示,“公司掌握Chiplet工艺技术,可以为客户提供晶圆级和基板级Chiplet封测解决方案,已为AMD大规模量产Chiplet产品,7nm产品已大规模量产,5nm产品已完成研发逐步量产,在国内的领先优势非常明显”。

华天科技是中国大陆排名前列的半导体封装测试公司,其表示,“公司Chiplet产品已经应用并量产,主要应用于5G通信、医疗、物联网等领域”。

长电科技则是世界第三、中国大陆第一的芯片封测龙头,业务覆盖了高中低各种集成电路封测。公司表示,公司XDFOIMChiplet高密度多维异构集成系列工艺已按计划进入稳定量产阶段,经过持续研发与客户产品验证,长电科技XIFOIM不断取得突破。

而在芯片设计等领域,寒武纪的思元370采用了chiplet技术;据媒体报道,华为2019年推出的7nm鲲鹏920处理器,也采用了Chiplet技术。

另外,在2022年12月,中国发布了首个原生Chiplet技术标准《小芯片接口总线技术要求》,将有助于行业的规范化、标准化发展,也是一个不小的进步。

国外巨头抢先布局

目前,台积电、英特尔、AMD等国际巨头相继布局 Chiplet。2022年3月,UCIe(UniversalChiplet Interconnect Express,通用芯粒互联技术)正式推出,旨在芯片封装层面确立互联互通的统一标准,打造一个开放性的 Chiplet 生态系统。

UCIe发起人为 Intel、AMD、ARM、高通、三星、台 积电、日月光、Google Cloud、Meta 和微软等十家公司,当前联盟成员包括Synopsys、Cadence、ADI、博通等国际龙头。目前,UCIe联盟为Chiplet制定了多种先进封装技术,包括英特尔EMIB、台积电CoWoS、日月光FoCoS-B等。

业内人士认为,UCIe推出后,各大厂商可以用同一个协议快速迭代,在解决Chiplet标准化方面具有划时代意义。

与此同时,国外巨头也相继推出相关产品。2023年1月11日,英特尔正式发布了基于Chiplet设计的第四代至强CPU-Sapphire Rapids,可将目标工作负载的平均每瓦性能提升了2.9倍,在最佳化电源模式下每个CPU节能可高达70瓦,将总体成本降低52%-66%。

Intel还发布了其首款Chiplet小芯片封装的GPU,代号Ponte Vecchio,GPU Max系列单个产品整合47个小芯片,内建超过1000亿个晶体管,综合实现了计算、存储、网络多项功能,将异构集成的技术提升至新水平。

台积电为Chiplet工艺的领军者,在其3DFabricTM技术平台下有CoWoS、InFO、SoIC三种封装工艺。其中,CoWoS工艺早在2016年就在英伟达TeslaP100AI数据中心GPU上得到应用。

今年,AMD推出的首款数据中心/HPC级的APU Instinct MI300,采用Chiplet技术,在4块6纳米芯片上,堆叠了9块5纳米的计算芯片。AMD表示,相较于上一代的Instinct MI250,提升了8倍的AI训练算力和5倍的AI能效。

而AMD最新一代的GPU Navi 31,是AMD第一款基于Chiplet设计的GPU。

资本支出远低于国际巨头

半导体产业是著名的“吞金”产业,需要持续的大量资金投入。Yole Developpement机构发布的一份数据显示,2021年半导体厂先进封装技术的资本支出排名中,前5名贡献了91%的资本支出,但没有一家中国大陆企业。

而国内的长电科技、通富微电则分列六、七位,相应的资本支出合计为9%,不及英特尔的三分之一。

在芯片堆叠、Chiplet等技术上,国外的晶圆厂可谓遥遥领先;而在封测环节,国内企业也明显落后于第一梯队,投入也远不及国际巨头。

国内Chiplet产业距离真正崛起,恐怕还任重道远。