大面积分析技术可以预防、探测和修复热点,从而将系统性、随机性和参数缺陷数量降至最低,并最终提高良率。

●通过虚拟工艺开发工具加速半导体工艺热点的识别

●这些技术可以节约芯片制造的成本、提升良率

设计规则检查 (DRC) 技术用于芯片设计,可确保以较高的良率制造出所需器件。设计规则通常根据所使用设备和工艺技术的限制和变异性制定。DRC可确保设计符合制造要求,且不会导致芯片故障或DRC违规。常见的DRC规则包括最小宽度和间隔要求、偏差检查以及其他规格,以避免在制造过程中出现短路、断路、材料过量或其他器件故障。

在先进的半导体技术节点,DRC规则的数量增加和复杂性提升,导致传统的2D DRC无法识别所有热点和故障。2D DRC无法模拟或预测3D规则违规,因此通常在开发晚期才能识别到3D故障。仅靠硅晶圆厂数据和测试宏来识别开发晚期的故障既耗时又昂贵。

泛林集团的SEMulator3D®虚拟制造平台可用于进行半导体器件的3D建模和基于规则的量测,并用比硅晶圆实验更快、更经济的方式识别热点(DRC违规)和潜在故障。

大面积分析 (Large Area Analysis) 是半导体工程研发中的重要概念,指为了探索大面积芯片区域内潜在热点的敏感性及其对下游工艺步骤的影响而进行的一系列实验。经过精心设计的大面积分析可以帮助工程师用较少的实验晶圆成本来开发出最佳的半导体工艺。

然而,大面积芯片区域潜在的工艺问题非常复杂,所以半导体设计和制造中的大面积分析(或实验)空间并没有被工程师充分挖掘。

本文中,我们将演示如何将SEMulator3D虚拟制造用于大面积分析,并通过在大面积模拟域中识别3D弱点展示我们的方法。

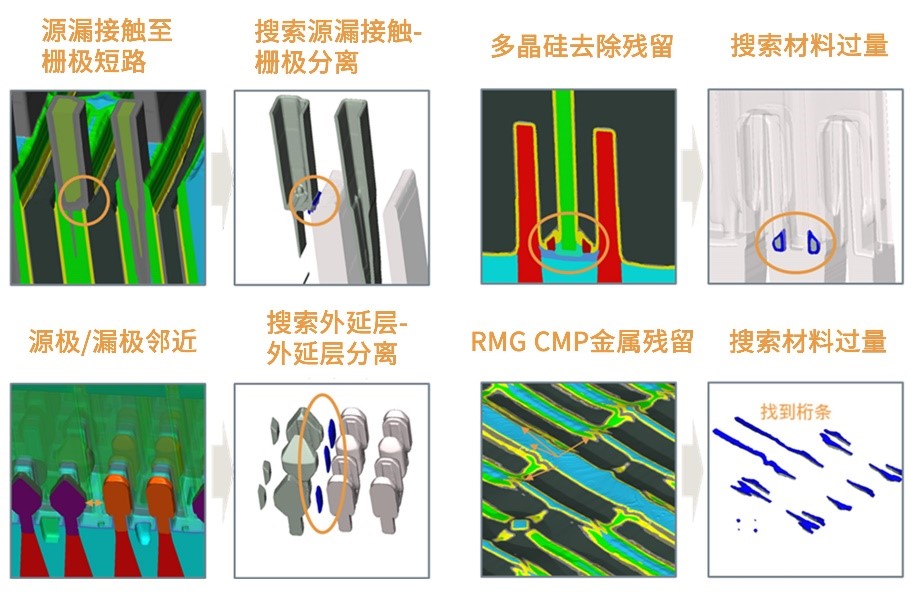

图1:使用SEMulator3D进行大面积分析

大面积3D DRC集成流程

图2是大面积分析3D DRC集成工艺图。其中包含三个输入值:SEMulator3D最佳已知方法工艺步骤模型、配置特定缺陷搜索标准的结构搜索宏和设计版图。

通过3D预测性工艺建模,SEMulator3D可以使用这些输入值来识别短路、断路、材料过量等3D器件故障。此模拟的输出值包括基于规则的量测、(搜索宏的)故障识别、以及缺陷图的生成。

大面积分析工艺结束后,用户可以查看整个大面积模拟域的测量结果。此外,还会生成包含潜在弱点的图形数据系统(GDS)版图文件,供进一步参考。

我们可以看到大面积分析3D DRC集成工艺的每个输出值,以及它们如何在半导体开发过程中加速热点和故障识别。

图2:大面积分析,3D DRC集成工艺图

3D结构搜索中基于规则的量测

通过对3D结构进行基于规则的虚拟量测,SEMulator3D中的3D模型可用于搜索和验证问题区域或热点。一旦有违反规则,软件会进行相应提示。而2D DRC工艺可能无法识别到所有这些违规——尽管使用简单的2D DRC可以识别某些热点,但由于2D DRC无法显示沉积、刻蚀或其他光刻工艺的变异性,所以结果并不完整。

3D工艺建模包括工艺和结构信息,可用于突显结构问题,比如绝缘距离太短、接触区域重叠或其他限制良率的设计问题(如图3)。在3D建模工艺中,可以建立几何标准,以研究各种器件特征的最小/最大关键尺寸,以及材料接口问题和其他器件研究。这些信息可用于协助工艺/设计的共同优化,并降低不可控性。通过在3D结构上进行虚拟且基于规则的量测,可以在开发早期、在硅晶圆厂数据和测试宏之前识别可能限制良率的故障。

图3:3D工艺建模中识别的故障类型

搜索宏和缺陷(热点)图

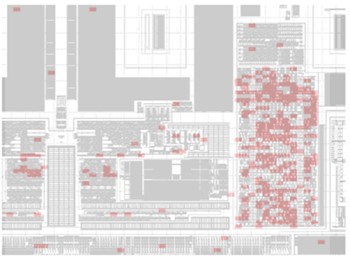

在SEMulator3D中,搜索宏可以识别大面积半导体区域内的违规或可能发生的器件故障。当搜索宏识别出故障时(使用基于规则的量测),会自动将结果输出到一个GDS文件(如图4),展示已识别故障的位置,该GDS文件包含在结构搜索工艺中识别的故障和缺陷。这些缺陷实际上是在3D结构中的,所以使用2D DRC方法通常无法识别它们。根据大面积研究中发现的缺陷类型,可能需要在SEMulator3D中进行工艺模型校准,以验证预测准确性。理论上,识别意外缺陷不需要先进的校准。

图4:大面积分析模拟的GDS文件,故障区域用红色标记

结论

在不需要晶圆实验的情况下识别工艺热点非常有价值:这不仅可以节省晶圆和掩膜成本,更重要的是,可以加速技术开发中的良率提升。

在最近使用SEMulator3D的项目中,大面积分析解决方案在开发早期识别出多个掩膜缺陷。其中,两个缺陷已经得到修正,并购买了新的掩膜。如果没有使用虚拟工艺开发工具,这种掩膜故障识别可能花费数月时间、数次试样的测试。

随着半导体技术的进步,大面积分析技术可以预防、探测和修复热点,从而将系统性、随机性和参数缺陷数量降至最低,并最终提高良率。对希望按时交付新半导体产品的企业来说,大面积分析用于探究制造可行性将成为成功的关键因素。