依照摩尔定律,全球半导体的工艺制程技术平均每两年进入一个新世代。从理性分析来看,业界都认为半导体业迟早会遇到技术上无法克服的物理极限,有人 说是10nm,也有人说是7nm甚至是5nm。极限在哪里,最终将由市场做出选择,它不仅受限于技术因素,还受成本等综合因素的限制,因为即使在技术上可 行,产品也未必能够受到业界的青睐。因此,目前为止权威人士预测,制程技术上的瓶颈可能出现在2018年左右。

14nm制程可能是个坎

14nm制程可能是个坎,采用三次图形曝光技术或EUV光刻技术。

缩小线路工艺尺寸和扩大硅片直径是推动半导体业不断地进步的“两个轮子”,然而,目前这两个轮子都遇到了障碍。

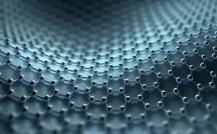

工艺微缩技术正面临瓶颈。从原理上分析,采用任何波长的光源都可以得到分辨率为1/3波长的特征图形。业界依此原理开发出将光源从248nm转变成 193nm的光刻设备,并用于65nm制程。另外又开发了多种提高分辨率的辅助技术,如相位移掩模版(PSMs),它是拓展193nm光刻能力的关键。 PSMs的继续发展将依赖于更强的相位移和更复杂的特征结构,目前最基本的是6%嵌入式的PSMs。

要使相位移技术达到下一代工艺水平要求,掩模版类型主要有三种:补偿式相位移、两次曝光图形和可以进行低k1成像的一次曝光技术。目前两次图形曝光 技术已趋于主流。之后设备厂开发出浸液式光刻技术,相当于将193nm波长缩短到134nm,从而提高了分辨率。业界试图找出比纯水折射指数更高的液体介 质,但至今仍未遂愿。

目前利用193nm浸液式光刻技术加上两次图形曝光技术等已经成功实现了20nm工艺技术的量产。业界一致认为下一代14nm制程可能是个坎,要么采用更复杂的三次图形曝光技术,但会大幅增加曝光次数及成本;要么采用革命性的EUV光刻技术。

不同解决方案各有利弊,各家公司都在做出选择。英特尔倾向于采用三次图形曝光技术,并认为有可能把193nm浸液式光刻技术延伸至10nm甚至 7nm。而IBM则坚信采用两次图形曝光技术可以缩小到10nm,并表示未来CMOS的尺寸缩小不会马上止步。至于EUV技术仍面临光源强度不够以及掩膜 版等配套材料需完善的问题。与此同时,其他多种光刻技术如电子束直写等也引起业界关注。

450mm设备厂积极性不高

受限于摩尔定律趋向终结等因素,450mm硅片可能会推迟更替。

硅片直径也不可能无限扩大。目前,硅片直径正由300mm向450mm过渡。从理性思维出发,硅片直径增大是迟早会被采用的,但至今为何未被市场接 受呢?可能有两方面原因:一是半导体设备厂的积极性不高,认为450mm设备200亿美元的研发成本可能无法收回;二是450mm硅片的建厂费用高达 100亿美元。目前对450mm制造厂有兴趣的厂商仅英特尔、三星及台积电三家。